FPGA內部IP核DDS

專案當中需要正弦訊號與餘弦訊號,首先想到了DDS晶片,例如AD9833、AD9834。由於還需要用FPGA 做一些資料處理,後來乾脆直接用FPGA 內部的DDSIP核,同時根據IP核內部的相位累加埠,設定觸發訊號,使得觸發訊號更加準時,並且通過PSD 演算法計算有效值,相位差更小,精度更高。

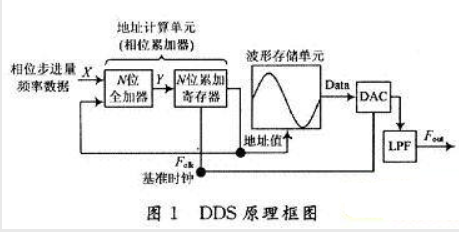

首先了解DDS的原理:

1、 DDS技術是根據奈奎斯特取樣定律,從連續訊號的相位出發,將正弦訊號取樣,編碼,量化,形成一個正弦函式表,存在EPROM中,合成時,通過改變相位累加器的頻率字來改變相位增量,也就是我們所稱的步長。相位增量的不同導致一個週期內取樣點的不同,在時鐘頻率即取樣頻率不變的情況下,通過相位的改變來改變頻率。

2、 DDS 以數控振盪器的方式,產生頻率、相位可控制的正弦,電路包括了基準時鐘源、相位累加器、相位調製器、正弦ROM 查詢表、D/A 轉換 器和低通濾波器等。 頻率控制字N 和相位控制字M 分別控制DDS 所輸出的正弦波的頻率和相 位。DDS 系統的核心是相位累加器,它由一個N 位累加器與N 位相位暫存器構成。時鐘脈衝每觸發一次, 累加器便將頻率控制資料與相位暫存器輸出的累加相位資料相加, 然後把相加後的結果送至相位暫存器的資料輸入端。 相位暫存器將累加器在上一個時鐘作用後所產生的新相位資料反饋到累加器的輸入端, 以使加法器在下一個時鐘的作用下繼續與頻率控制資料相加。 這樣, 相位累加器在參考時鐘的作用下將進行線性相位累加, 當相位累加器累加滿時, 就會產生一次溢位, 以完成一個週期性的動作, 這個週期就是DDS 合成訊號的一個頻率週期, 相位累加器的溢位頻率就是DDS 輸出的訊號頻率。 相位暫存器的輸出與相位控制字相加, 結果作為正弦查詢表的地址。 查詢表由ROM 構成, 其內部存有一個完整週期正弦波的數字幅度資訊, 每個查詢表的地址對應正弦波中的一個相位點。 查詢表把輸入地址資訊對映成正弦波幅度訊號, 同時輸出到D/A 轉換器的輸入端, 通過D/A 可將數字量形式的波形幅值轉換成所要求的合成頻率模擬量形式訊號。 低通濾波器用於衰減和濾除不需要的取樣分量, 以便輸出頻譜純淨的正弦波訊號。

ISE DDS IP核設定如下圖,輸出正弦訊號為12位,為了實現頻率的高解析度,需要將相位增加足夠的小,因此相位寬度為33位。

相關推薦

FPGA內部IP核DDS

專案當中需要正弦訊號與餘弦訊號,首先想到了DDS晶片,例如AD9833、AD9834。由於還需要用FPGA 做一些資料處理,後來乾脆直接用FPGA 內部的DDSIP核,同時根據IP核內部的相位累加埠,設定觸發訊號,使得觸發訊號更加準時,並且通過PSD 演算法計算有效值,

關於ISE無法生成DDS IP核的問題

直接上error: "E:/*/ipcore_dir/tmp/./_cg/_dbg/./dds_compiler_v4_0/sin_cos.vhd" line 228: Real operand is not supported in this context. ERROR:sim -ERROR

FPGA-ip核的使用

IP核(IP Core) ISE中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、訊號處理(FFT、DFT、DDS等)。IP核類似程式設計中的函式庫(例如C語言中的printf()函式),可以直接呼叫,非常方便,大大加

FPGA數字訊號處理(五)Vivado FIR IP核實現

該篇是FPGA數字訊號處理的第五篇,選題為DSP系統中極其常用的FIR濾波器。本文將在前三篇的基礎上,繼續介紹在Vivado開發環境下使用Xilinx提供的FIR IP核進行FIR濾波器的設計。 IP核概述 Xilinx的FIR IP核屬於收費I

利用IP核設計高性能的計數器

1-1 開始 信號 軟件 需要 模式 counter put always 利用Quartus II的LPM_counter IP核進行設計(利用IP核設計可以迅速高效的完成產品的設計) 新建工程 調用IP核 創建一個新的IP核 選擇LMP_COUNT

IP核之初——FIFO

規範 初學者 傳輸 分享 png 初學 架構 人的 內部 本文設計思路源自明德揚至簡設計法。在之前的幾篇博文中,由於設計比較簡單,所有的功能都是用verilogHDL代碼編寫實現的。我們要學會站在巨人的肩膀上,這時候就該IP核登場了! 說白了,IP核就是別人做好了的

Xilinx DDR3 IP核使用問題匯總(持續更新)和感悟

amp per uid gravity 流程 vhdl ade 官方 vhd 一度因為DDR3的IP核使用而發狂。 後來因為解決問題,得一感悟。後面此貼會完整講述ddr3 ip的使用。(XILINX K7) 感悟:對於有供應商支持的產品,遇到問題找官方的流程。按照官方的指導

Vivado使用技巧:封裝自己設計的IP核

開源 創建 pre 範圍 輸入 sign 分享圖片 出了 face 概述 ??Vivado在設計時可以感覺到一種趨勢,它鼓勵用IP核的方式進行設計。“IP Integrator”提供了原理圖設計的方式,只需要在其中調用設計好的IP核連線。IP核一部分來自於Xilinx官方I

AXI-Lite總線及其自定義IP核使用分析總結

定義 ip核 create 自定義 valid 圖片 打開 pro man ZYNQ的優勢在於通過高效的接口總線組成了ARM+FPGA的架構。我認為兩者是互為底層的,當進行算法驗證時,ARM端現有的硬件控制器和庫函數可以很方便地連接外設,而不像FPGA設計那樣完全寫出接

[轉]Vivado IP核生成設置

with edi exp doc 一個 設置 輸入輸出 一起 生成 vivado中design with ip相比於ise感覺還是改進了。 首先我們簡單介紹一下vivado中design with ip的設計過程: (1)打開IP Catlog定制

Google開源新的 RISC-V IP核: “BottleRocket”(https://cnrv.io)

-s git link ilog 配置 三級 ttl github 非官方 BottleRocket是RISCV RV32IMC的實現。 Google在2017年11月29日在Github上非官方開源了BottleRocket的RTL代碼,同時表明這並不是一個官方支持的G

IP核之初——FIFO添加以太網MAC頭部

準備 說明 bar 成了 別人 實現 mac地址 第一個 scale 說白了,IP核就是別人做好了的硬件模塊,提供完整的用戶接口和說明文檔,更復雜的還有示例工程,你只要能用好這個IP核,設計已經完成一半了。說起來容易,從冗長的英文文檔和網上各個非標準教程中汲取所需,並靈活運

如何將自己寫的verilog模塊封裝成IP核

目錄 第二篇 hierarchy 布局 options ssi campaign mac sed 如何將自己寫的verilog模塊封裝成IP核 (2014-11-21 14:53:29) 轉載▼ 標簽: 財經 分類: 我的東東 ========

Xilinx Vivado的使用詳細介紹(5):調用用戶自定義封裝的IP核

cond 5.4 vba adding 計算機 property with 我們 class Zedboard OLED Display Controller IP v1 介紹

vivado中使用ROM IP核

-- .com inf init lock amp 寬度 project img 1.在project中選擇IP Catalog 在IP Catalog中選擇---->Block Memory Generator------>RAMs&ROMs&

自定義AXI-IP核(轉)

目的: 自定義一個IP核,通過AXI匯流排與ARM系統連線 環境: Win7 32bit Vivado2014.4.1 Xilinx sdk2014.4 開發板: Zc702 &nbs

理解AXI Quad Serial Peripheral Interface(SPI) IP核

在使用MicroBlaze過程中,呼叫了此IP,所以有必須仔細學習下; 名詞: XIP: eXecute In Place Motorola M68HC11 支援特性:

Xilinx 濾波器IP核輸出有效位擷取問題

Xilinx是按照如下公式給出輸出位寬的: outputwidth = coefwidth + inputwidth + ceil(log2(tap)) 其中,outputwidth即為輸出位寬,coefwidth為抽頭係數位寬,inputwidth為輸入位寬,tap為濾波器階數,ceil為

Vivado HLS實現FIR濾波器(2)——Vivado呼叫HLS生成的FIR IP核

系統框圖 器件xq7a50tfg484-2I,兩個DDS,輸入時鐘100MHz,輸出分別為8MHz和12MHz,位寬為16位,相乘後輸出位寬32位,三角函式積化和差得4MHz訊號和20MHz訊號,濾波器設計採用Filter Solutions 2015,截止頻率10MHz,取樣率10

1. FPGA內部的邏輯資源

CLB(包括LUT、加法器、暫存器、MUX(多路選擇器)) 時鐘網路資源(全域性時鐘網路,區域時鐘網路,IO時鐘網路),理解時鐘網路的本質和意義 時鐘處理單元(PLL,DCM),理解時鐘網路資源和時鐘處理單元的差異和相關性 BLOCK RAM:用於快取資料 DSP核 介面資源:對於FPGA而言,IO