SPI總線 通俗易懂講解——(轉載)

SPI總線

MOTOROLA公司的SPI總線的基本信號線為3根傳輸線,即SI、SO、SCK。傳輸的速率由時鐘信號SCK決定,SI為數據輸入、SO為數據輸出。采用SPI總線的系統如圖8-27所示,它包含了一個主片和多個從片,主片通過發出片選信號-CS來控制對哪個從片進行通信,當某個從片的-CS信號有效時,能通過SI接收指令、數據,並通過SO發回數據。而未被選中的從片的SO端處於高阻狀態。

圖8-27 SPI總線的系統

圖8-27 SPI總線的系統

主片在訪問某一從片時,必須使該從片的片選信號有效;主片在SCK信號的同步下,通過SI線發出指令、地址信息;如需將數據輸出,則接著寫指令,由SCK同步在SI線上發出數據;如需讀回數據,則接著讀指令,由主片發出SCK,從片根據SCK的節拍通過SO發回數據。

因而對具有SPI接口的從片器件來講,SCK、SI是輸入信號,SO是輸出信號。SCK用於主片和從片通信的同步。SI用於將信息傳輸到器件,輸入的信息包括指令、地址和數據,指令、地址和數據的變化在SCK的低電平期間進行,並由SCK信號的上升沿鎖存。SO用於將信息從器件傳出,傳出的信息包括狀態和數據,信息在SCK信號的下降沿移出。

Microchip公司的25XX系列的串行E2PROM采用了SPI總線,該系列器件的性能如表8-2所示。

| 型號 | 25XX040 | 25XX080 | 25XX160 | 25XX320 |

| 容量 | 4K (512 X 8bit) | 8K (1024 X 8bit) | 16K (4096 X 8bit) | 32K (4096 X 8bit) |

| 地址信號 | A0~A8 | A0~A9 | A0~A10 | A0~A11 |

以25XX320為例,該器件是4K字節的E2PROM,結構如圖8-28所示,接口信號為SCK、SI和SO,此外還具有-CS、-WP、-HOLD信號線。其中-CS為器件選中信號,當此信號為低電平時器件被選中,高電平時器件處於等待狀態。

圖8-28 25XX320的結構

圖8-28 25XX320的結構

與並行接口電路不同的是,在並行接口電路中對器件進行操作的控制信號,在串行接口電路中只能用指令實現,25XX320的操作指令有數據讀指令、寫操作的允許和禁止指令、寫數據指令和狀態寄存器的讀寫指令。在器件的內部有一個8位的指令寄存器,在SCK的上升沿,通過SI信號線,指令輸入到上述寄存器並被執行。

表8-3 25系列串行存儲器的指令

| 指令名稱 | 指令格式 | 描述 |

| READ | 00000011 | 從選定的地址開始讀存儲器數據 |

| WRITE | 00000010 | 從選定的地址開始寫存儲器數據 |

| WRDI | 00000100 | 禁止寫操作 |

| WREN | 00000110 | 允許寫操作 |

| RDSR | 00000101 | 讀狀態寄存器 |

| WRSR | 00000001 | 寫狀態寄存器 |

器件的讀操作時序如圖8-29所示。當-CS信號有效時,在SCK信號的同步下,8位的讀指令送入器件,接著送入16位地址(由於25XX320只使用地址信號A0~A11,地址的高4位無效)。在讀指令和地址發出後,SCK繼續發出時鐘信號,此時存儲在該地址的數據由SCK控制從SO引腳移出。在每個數據移出後,內部的地址指針自動加1,如繼續對器件發送SCK信號,可讀出下一個數據。當地址指針計到0FFFH之後,將回到0000H。讀操作的結束由-CS信號變高實現。

圖8-29 25系列串行存儲器的讀時序

圖8-29 25系列串行存儲器的讀時序

25XX系列的串行EEPROM的寫操作通過寫允許及禁止指令控制,寫操作必須在器件處於寫允許狀態時進行。

寫允許及禁止指令均為8位的指令,指令的操作過程為:將-CS信號置為低電平,在SCK信號的作用下,通過SI引腳輸入上述指令,在8位的指令送入器件之後,將-CS信號置為高電平,使器件鎖存於寫允許或寫禁止狀態。如在輸入寫允許指令後未將-CS信號置為高電平,則寫允許狀態未鎖存,此時如直接進行寫操作,數據將不能寫入存儲器。在上電、寫禁止指令、寫狀態寄存器指令、寫數據指令執行之後,器件的寫允許狀態將被復位,即處於寫禁止狀態。

寫操作通常在寫允許指令之後進行,其時序如圖8-30所示。在寫允許狀態鎖存後,將-CS變高;再將-CS變低,在SCK的同步下輸入寫操作指令並送入16位地址,緊接著發送需寫入的數據,寫入的數據一次最多可達32個,但必須保證在同一頁內。一頁數據的地址從XXXXXXXX

XXX0 0000 開始,到XXXX XXXX XXX1 1111結束,當內部的地址指針計數器達到XXXX

XXXX XXX11111後,繼續發送時鐘信號將使地址計數器回復到該頁的第一個地址,即XXXX XXXX XXX0 0000H。

圖8-30 25系列串行存儲器的寫時序

圖8-30 25系列串行存儲器的寫時序

為了使數據有效寫入,-CS信號只能在寫入數據的最後一個字節的最低位寫入後變高。如-CS信號在其他時間變高,將無法保證數據的完整寫入。在寫操作的過程中,能通過讀狀態指令將狀態寄存器的內容讀回,當寫操作完成後,寫允許鎖存狀態將被復位。

優缺點

SPI接口具有如下

優點:

1) 支持全雙工操作;

2) 操作簡單;

3) 數據傳輸速率較高。

缺點:

1) 需要占用主機較多的口線(每個從機都需要一根片選線);

2) 只支持單個主機。

3) 沒有指定的流控制,沒有應答機制確認是否接收到數據。

如果還是看不懂,那就再通俗點。

SPI總線協議介紹

一、技術性能

SPI接口是Motorola

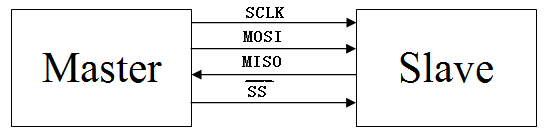

首先提出的全雙工三線同步串行外圍接口,采用主從模式(MasterSlave)架構;支持多slave模式應用,一般僅支持單Master。時鐘由Master控制,在時鐘移位脈沖下,數據按位傳輸,高位在前,低位在後(MSBfirst);SPI接口有2根單向數據線,為全雙工通信,目前應用中的數據速率可達幾Mbps的水平。總線結構如下圖所示。

二、接口定義

SPI接口共有4根信號線,分別是:設備選擇線、時鐘線、串行輸出數據線、串行輸入數據線。

(1)MOSI:主器件數據輸出,從器件數據輸入

(2)MISO:主器件數據輸入,從器件數據輸出

(3)SCLK:時鐘信號,由主器件產生

(4)/SS:從器件使能信號,由主器件控制

三、內部結構

四、 時鐘極性和時鐘相位

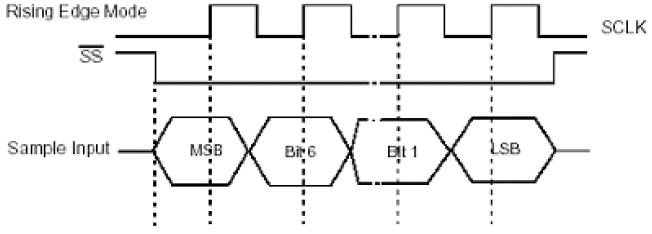

在SPI操作中,最重要的兩項設置就是時鐘極性(CPOL或UCCKPL)和時鐘相位(CPHA或UCCKPH)。時鐘極性設置時鐘空閑時的電平,時鐘相位設置讀取數據和發送數據的時鐘沿。

主機和從機的發送數據是同時完成的,兩者的接收數據也是同時完成的。所以為了保證主從機正確通信,應使得它們的SPI具有相同的時鐘極性和時鐘相位。

SPI接口時鐘配置心得:在主設備這邊配置SPI接口時鐘的時候一定要弄清楚從設備的時鐘要求,因為主設備這邊的時鐘極性和相位都是以從設備為基準的。因此在時鐘極性的配置上一定要搞清楚從設備是在時鐘的上升沿還是下降沿接收數據,是在時鐘的下降沿還是上升沿輸出數據。

五、傳輸時序

SPI接口在內部硬件實際上是兩個簡單的移位寄存器,傳輸的數據為8位,在主器件產生的從器件使能信號和移位脈沖下,按位傳輸,高位在前,低位在後。如下圖所示,在SCLK的下降沿上數據改變,上升沿一位數據被存入移位寄存器。

五、數據傳輸

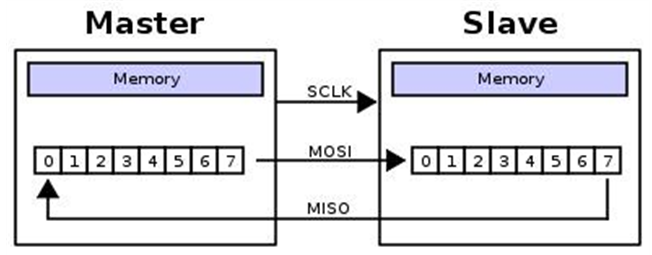

在一個SPI時鐘周期內,會完成如下操作:

1)主機通過MOSI線發送1位數據,從機通過該線讀取這1位數據;

2)從機通過MISO線發送1位數據,主機通過該線讀取這1位數據。

這是通過移位寄存器來實現的。如下圖所示,主機和從機各有一個移位寄存器,且二者連接成環。隨著時鐘脈沖,數據按照從高位到低位的方式依次移出主機寄存器和從機寄存器,並且依次移入從機寄存器和主機寄存器。當寄存器中的內容全部移出時,相當於完成了兩個寄存器內容的交換。

SPI總線 通俗易懂講解——(轉載)