SylixOS SPI 總線框架淺析

阿新 • • 發佈:2018-09-05

有效 usb image water typedef truct atomic 創建 操作 修訂歷史

版本 日期 原因

V1.00 2018/8/18 創建文檔

版本 日期 原因

V1.00 2018/8/18 創建文檔

目 錄

1 SPI總線關鍵結構體 1

1.1 總線傳輸控制消息塊 1

1.2 SPI總線適配器 2

1.3 SPI設備 3

2 SPI各個結構體之間的聯系 3

2.1 總線鏈表 3

2.2 總線與設備 3

3 參考資料 4

1 SPI總線關鍵結構體

1.1 總線傳輸控制消息塊

傳輸控制消息包括操作單位bits數、傳輸控制參數(時鐘極性、相位和字節序等配置)、發送和接收緩沖區及其長度、傳輸結束的回調函數。如程序清單 1.1所示。

程序清單 1.1

typedef struct lw_spi_message { UINT16 SPIMSG_usBitsPerOp; /* 操作單位bits數 */ UINT16 SPIMSG_usFlag; /* 傳輸控制參數 */ #define LW_SPI_M_CPOL_0 0x0000 /* CPOL 配置 */ #define LW_SPI_M_CPOL_1 0x0001 #define LW_SPI_M_CPHA_0 0x0000 /* CPHA 配置 */ #define LW_SPI_M_CPHA_1 0x0002 #define LW_SPI_M_CPOL_EN 0x0004 /* 是否設置新的 CPOL 配置 */ /* 否則 CPOL 配置與上次傳輸相同*/ #define LW_SPI_M_CPHA_EN 0x0008 /* 是否設置新的 CPHA 配置 */ /* 否則 CPHA 配置與上次傳輸相同*/ /********************************************************************************************************* LW_SPI_M_WRBUF_FIX, LW_SPI_M_RDBUF_FIX 主要用於半雙工的 SPI 操作 (多數從機器件都是這種操作模式). 1: 當 LW_SPI_M_WRBUF_FIX 有效時, 表明本次操作是讀操作, 每次發送的數據都是 SPIMSG_pucWrBuffer 的第一個字 符, 而讀到的數據將依次存放在 SPIMSG_pucRdBuffer 中. 所以: 讀緩沖的大小必須可以存放 SPIMSG_usLen 個字符, 而寫緩沖的大小可以僅是 1 個字符長度. 2: 當 LW_SPI_M_RDBUF_FIX 有效時, 表明本次操作是寫操作, 對讀到什麽數據並不感興趣, 所以每次讀到的數據都放 在 SPIMSG_pucRdBuffer 的第一個字符處. 所以: 寫緩沖的大小必須可以存放 SPIMSG_usLen 個字符, 而讀緩沖的大小可以僅是 1 個字符長度. *********************************************************************************************************/ #define LW_SPI_M_WRBUF_FIX 0x0010 /* 發送緩沖區僅發送第一個字符 */ /* 永遠發送第一個字符 */ #define LW_SPI_M_RDBUF_FIX 0x0020 /* 接收緩沖區僅接收第一個字符 */ /* 接收的數據永遠發在第一個接收*/ /* 緩沖指針的位置 */ #define LW_SPI_M_MSB 0x0040 /* 從高位到低位 */ #define LW_SPI_M_LSB 0x0080 /* 從低位到高位 */ UINT32 SPIMSG_uiLen; /* 長度(緩沖區大小) */ /* 長度為0, 只設置傳輸控制參數 */ UINT8 *SPIMSG_pucWrBuffer; /* 發送緩沖區 */ UINT8 *SPIMSG_pucRdBuffer; /* 接收緩沖區 */ VOIDFUNCPTR SPIMSG_pfuncComplete; /* 傳輸結束後的回調函數 */ PVOID SPIMSG_pvContext; /* 回調函數參數 */ } LW_SPI_MESSAGE;

1.2 SPI總線適配器

總線設配器包括總線節點、總線適配器操作函數、總線操作鎖和設備鏈表。如程序清單 1.2所示。總線節點是用於管理所有SPI總線的鏈表節點;總線適配器操作函數包括總線傳輸函數和總線控制函數;總線操作鎖用於實現總線互斥操作;設備鏈表是由所有關聯當前SPI適配器的設備組成的鏈表。

程序清單 1.2

typedef struct lw_spi_adapter { LW_BUS_ADAPTER SPIADAPTER_pbusadapter; /* 總線節點 */ struct lw_spi_funcs *SPIADAPTER_pspifunc; /* 總線適配器操作函數 */ LW_OBJECT_HANDLE SPIADAPTER_hBusLock; /* 總線操作鎖*/ LW_LIST_LINE_HEADER SPIADAPTER_plineDevHeader; /* 設備鏈表 */ } LW_SPI_ADAPTER; typedef struct lw_spi_funcs { INT (*SPIFUNC_pfuncMasterXfer)(PLW_SPI_ADAPTER pspiadapter, PLW_SPI_MESSAGE pspimsg, INT iNum); /* 適配器數據傳輸 */ INT (*SPIFUNC_pfuncMasterCtl)(PLW_SPI_ADAPTER pspiadapter, INT iCmd, LONG lArg); /* 適配器控制 */ } LW_SPI_FUNCS;

1.3 SPI設備

SPI設備結構成員包括掛載的適配器指針、設備掛載鏈、設備使用計數、設備名稱。如程序清單 1.3所示。

程序清單 1.3

typedef struct lw_spi_device { PLW_SPI_ADAPTER SPIDEV_pspiadapter; /* 掛載的適配器 */ LW_LIST_LINE SPIDEV_lineManage; /* 設備掛載鏈 */ atomic_t SPIDEV_atomicUsageCnt; /* 設備使用計數 */ CHAR SPIDEV_cName[LW_CFG_OBJECT_NAME_SIZE]; /* 設備的名稱 */ } LW_SPI_DEVICE;

2 SPI各個結構體之間的聯系

2.1 總線鏈表

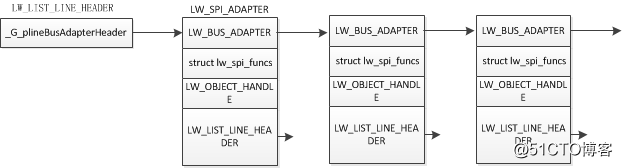

所有SPI總線適配器都是鏈接在以_G_plineBusAdapterHeader為頭節點的鏈表上。如圖 2.1所示。

圖 2.1 SPI總線鏈表

2.2 總線與設備

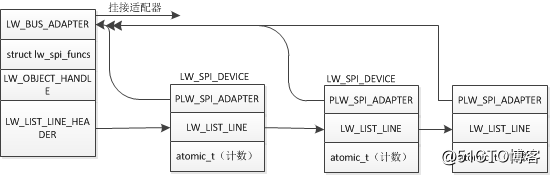

總線與設備的邏輯關系如圖 2.2所示。

圖 2.2 總線與設備關系

3 參考資料

《SylixOS_driver_usermanual》

SylixOS SPI 總線框架淺析