上拉電阻、下拉電阻、拉電流、灌電流、扇出係數等基本概念

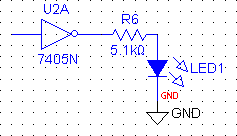

在使用數字積體電路時,拉電流輸出和灌電流輸出是一個很重要的概念,例如在使用反向器作輸出顯示時,圖1是拉電流,即當輸出端為高電平時才符合發光二極體正向連線的要求,但這種拉電流輸出對於反向器只能輸出零點幾毫安的電流用這種方法想驅動二極體發光是不合理的(因發光二極體正常工作電流為5~10mA)。

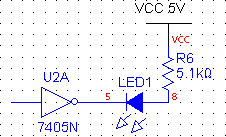

圖2為灌電流輸出,即當反向器輸出端為低電平時,發光二極體處於正向連線情況,在這種情況下,反向器一般能輸出5~10mA的電流,足以使發光二極體發光,所以這種灌電流輸出作為驅動發光二極體的電路是比較合理的。因為發光二極體發光時,電流是由電源+5V通過限流電阻R、發光二極體流入反向器輸出端,好像往反向器裡灌電流一樣,因此習慣上稱它為“灌電流”輸出。

==============================================================================================================================

淺談上、下拉電阻的作用什麼是拉電流和灌電流

上下拉電阻:

1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低於COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

2、OC閘電路必須加上拉電阻,以提高輸出的高電平值。

3、為加大輸出引腳的驅動能力,有的微控制器管腳上也常使用上拉電阻。

4、在COMS晶片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產生降低輸入阻抗,提供洩荷通路。

5、晶片的管腳加上拉電阻來提高輸出電平,從而提高晶片輸入訊號的噪聲容限增強抗干擾能力。

6、提高匯流排的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。

7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

上拉電阻阻值的選擇原則包括:

1、從節約功耗及晶片的灌電流能力考慮應當足夠大;電阻大,電流小。

2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。

3、對於高速電路,過大的上拉電阻可能邊沿變平緩。綜合考慮

以上三點,通常在1k到10k之間選取。對下拉電阻也有類似道理

電阻的具體取值怎麼計算的?

上拉電阻是不是應該是接Vcc再接電阻,然後接到管腳上的?

一般上下拉的電阻取值都有個特定的範圍,不能太大,也不能太小.都在幾K到幾十K之間吧,具體的還要看電路要求.

至於接法,上拉電阻簡單來說就是把電平拉高,通常用4.7-10K的電阻接到Vcc電源,下拉電阻則是把電平拉低,電阻接到GND地線上。所以是接電源或者接地,再接到需要拉高或者拉地電平的節點上的.

一般說來,不光是重要的訊號線,只要訊號在一段時間內可能出於無驅動狀態,就需要處理。

比如說,一個CMOS門的輸入端阻抗很高,沒有處理,在懸空狀況下很容易撿拾到干擾,如果能量足夠甚至會導致擊穿或者閂鎖,導致器件失效。祈禱輸入的保護二極體安全工作吧。如果電平一直處於中間態,那輸出就可能是不確定的情況,也可能是上下MOS都導通,對器件壽命造成影響。

總線上當所有的器件都處於高阻態時也容易有干擾出現。因為這時讀寫控制線處於無效狀態,所以不一定會引起問題。你如果覺得自己能夠接受的話也就將就了。但是這時你就要注意到,控制線不能懸空,不然……

TTL電路的輸入端是一個發射極開路引出的結構,拉高或者不接都是高電平,但是強烈建議不要懸空不接。

上拉還是下拉?要看需要。一方面器件可能又要求,另一方面,比如總線上兩個器件,使能控制都是高有效,那麼最好下拉,否則當控制訊號沒有建立的時候就會出現兩個衝突,可能燒片。如果計算機總線上面掛了一個D/A,上電覆位訊號要對它清零或者預置,那麼匯流排可以上下拉到你需要的數字。

至於上下拉電阻的大小,這個情況就比較多了。CMOS輸入的阻抗很高,上下拉電阻阻值可以大一些,一般低功耗電路的阻值取得都比較大,但是抗干擾能力相應比較弱一些。

很多場合下拉電阻取值比上拉電阻要小,這個是歷史遺留問題。如上面所說,TTL電路上拉時輸入3集管基射反偏,沒有什麼電流,但是下拉時要能夠使得輸入電晶體工作,這個在TTL的手冊中可以查到。

也是為了這個歷史遺留問題,有些CMOS器件內部採用了上拉,這時它會告訴你可以不處理這些管腳,但是這時你就要注意了,因為下拉再用10K可能不好使,因為也許內建的20K電阻和外接的10K把電平固定在了1V左右。

有時候你會看到150歐姆或者50歐姆左右的上下拉電阻,尤其是在高速電路中會看到。

150歐姆電阻下拉一般在PECL邏輯中出現。PECL邏輯輸出級是設計開路的電壓跟隨器,需要你用電阻來建立電壓。

50歐姆的電阻在TTL電路中用的不多,因為靜態功耗實在是比較大。在CML電路和PECL電路中兼起到了端接和偏置的作用。

CML電路輸出級是一對集電極開路的三極體,需要一個上拉電阻來建立電平。這個電阻可以放在傳送端,那麼接受端還需要端接處理,也可以放到接受端,這時候端接電阻和偏置電阻就是一個。PECL電路結構上就好像CML後面跟了一個射極跟隨器。

OC門也使用上拉電阻,這個和CML有一點相像,但是還不太一樣。CML和PECL電路中三極體工作線上形區,而普通閘電路和OC/OD門工作在飽和區。OC/OD閘電路常用作電平轉換或者驅動,但是其工作速度不會太快。為什麼?在OC/OD門中,上拉電阻不能太小,否則功耗會很大。而一般門的負載呈現出一個電容,負載越多,電容越大。當由高到低跳變時,電容的放電通過輸出端下拉的MOS或者Bipolar管驅動,速度一般還是比較快的,但是由低到高跳變的時候,就需要通過上拉電阻來完成,R大了幾十甚至上百倍,假設C不變,時間常數相應增加同樣的倍數。這個在示波器上也可以明顯的看出:上升時間比下降時間慢了很多。其實一般閘電路上拉比下拉的驅動能力都會差一些,這個現象都存在,只不過不太明顯罷了?

在匯流排的上下拉電阻設計中,就要考慮同樣的問題了:總線上往往負載很重,如果你要電阻來提供一些值,你就必須保證電容能通過電阻在一定時間內放電到可接受的範圍。如果電阻太大,那麼就可能出錯。

PLD可程式設計上下拉,還有匯流排保持也相當於上下拉,可以省去外接電阻。但是有一些麻煩。

一般輸入端才需要上下拉,假設器件10K是一個可行的值,那麼10個元件並聯會等效有多大的輸入上拉電阻?1K。

也就是說,如果你想給訊號線預置一個低電平,可能需要200歐姆的外接下拉電阻。這種情況下,如果還有一個3門驅動這個訊號,高電平的時候需要扇出15mA左右的靜態電流,有點太大了。這就是附加的負載效應。

如果兩個器件一個上拉一個下拉,當一個3態門驅動,輸出3態時會怎麼樣?電平1.5V左右,兩個門處於不高不低的狀態,預置電平的目的沒有達到,而且可能誘發震盪,對器件壽命造成影響。

內建上下拉電阻使得設計可靠的電路複雜性增加了,一個不留神就可能留下隱患,而且很難分析,使用中要非常非常小心。如果能夠外接電阻,儘量還是少採用內建上下拉或者匯流排保持的閘電路吧。

電阻的上拉與下拉

在網上看到一些對電阻的上拉和下拉不太明白的,輸入端的上拉及下拉非常簡單但也非常重要。

上拉:通過一個電阻對電源相連。

下拉:通過一個電阻到地。

上下拉一般有兩個用處:提高輸出訊號的驅動能力、確定輸入訊號的電平(防止干擾)。

用過8051的都知道CPU的I/O上通常接有排阻(上拉到5V),這裡主要是為了提高輸出驅動能力的。因為8051的CPU不是標準的I/O口,輸出為低電平時可以吸收均20mA的電流,但輸出為高的時候是通過內部一個很大的電阻上拉的,輸出高電平時驅動能力很差,所以就通過外部上拉來提高電平輸出驅動能力。

一般一個三極體的基極都有兩個電阻,一個限流一個上拉或下拉,此處的上下拉主要為了確定輸入訊號的電平。其實目標是為了防止干擾,因為器件的輸入介面一般內阻都很大,很容易受干擾。接一個上下拉電阻其實也就是降低了輸入阻抗,提高了抗干擾能力。

一般元器件不用的輸入口通要求接上拉或下拉電阻。注意,不用的輸出介面就不要接東西了。

拉電流和灌電流就是從晶片外電路通過引腳流入晶片內的電流,區別在於吸收電流是主動的,從晶片輸入端流入的叫拉電流,灌入電流是被動的,從輸出端流入的叫灌入電流。

上拉和下拉的區別是一個為拉電流,一個為灌電流

一般來說灌電流比拉電流要大

也就是灌電流驅動能力強一些

當邏輯閘輸出端是低電平時,灌入邏輯閘的電流稱為灌電流,灌電流越大,輸出端的低電平就越高。由三極體輸出特性曲線也可以看出,灌電流越大,飽和壓降越大,低電平越大。邏輯閘的低電平是有一定限制的,它有一個最大值UOLMAX。在邏輯閘工作時,不允許超過這個數值,TTL邏輯閘的規範規定UOLMAX ≤0.4~0.5V。

當邏輯閘輸出端是高電平時,邏輯閘輸出端的電流是從邏輯閘中流出,這個電流稱為拉電流。拉電流越大,輸出端的高電平就越低。這是因為輸出級三極體是有內阻的,內阻上的電壓降會使輸出電壓下降。拉電流越大,高電平越低。邏輯閘的高電平是有一定限制的,它有一個最小值UOHMIN。在邏輯閘工作時,不允許超過這個數值,TTL邏輯閘的規範規定UOHMIN ≥2.4V。

由於高電平輸入電流很小,在微安級,一般可以不必考慮,低電平電流較大,在毫安級。所以,往往低電平的灌電流不超標就不會有問題,用扇出係數來說明邏輯閘來同類門的能力。扇出係數No是低電平最大輸出電流和低電平最大輸入電流的比值

對於標準TTL門,NO≥10;對於低功耗肖特基系列的TTL門,NO≥20