System Generator從入門到放棄(三)-Digital Filter

System Generator從入門到放棄(三)-Digital Filter

本文轉自:https://blog.csdn.net/fpgadesigner/article/category/6985565/3

文章目錄

- System Generator從入門到放棄(三)-Digital Filter

- 一、Digital Filter

- 1、簡介

- 2、產生正弦訊號

- 3、數字濾波器的設計

- 4、FDATool block的使用

- 5、生成說明文件與testbench

- 6、資源分析與時序分析

- 7、Gateway In和Gateway Out詳解

- 8、設計優化與匯入MATLAB變數

- 9、選擇最佳資料型別

- 10、Reinterpret和Convert詳解

System Generator是Xilinx公司進行數字訊號處理開發的一種設計工具,它通過將Xilinx開發的一些模組嵌入到Simulink的庫中,可以在Simulink中進行定點模擬,可以設定定點訊號的型別,這樣就可以比較定點模擬與浮點模擬的區別。並且可以生成HDL檔案,或者網表,可以在ISE中進行呼叫。或者直接生成位元流下載檔案。能夠加快DSP系統的開發進度。

一、Digital Filter

1、簡介

2、產生正弦訊號

2.1 本部分設計使用到的block

3、數字濾波器的設計

3.1 本部分設計使用到的block

3.2 數字濾波器設計

3.3 FPGA系統配置

3.4 將設計匯出到FPGA

3.5 開啟Vivado示例工程

4、FDATool block的使用

5、生成說明文件與testbench

5.1 生成說明文件

5.2 生成testbench

6、資源分析與時序分析

6.1 檢視分析結果

6.2 時序分析

6.3 資源分析

6.4 資時序/資源分析失敗的說明

以上內容請移步

https://blog.csdn.net/Pieces_thinking/article/details/83656785

7、Gateway In和Gateway Out詳解

7.1 Simulink到FPGA的轉換

Simulink中的模擬模型為連續時間系統,資料格式多種多樣;而FPGA中為離散時間系統,資料必須用一定的位數進行量化。兩者之間必須要進行從連續到離散的轉換、資料格式的轉換,否則無法進行正確的FPGA設計。Xilinx Blockset中提供了相應的解決方案。

Gateway In和Gateway Out這兩個block便是Simulink與FPGA之間的轉換介面。經過轉換後,Gateway In對應的是HDL模型中input;Gateway Out對應的是HDL模型中的output。可以說,所有的System Generator設計中必須包含至少一個Gateway In和Gateway Out。

7.2 Gateway In block

7.2.1 資料型別轉換

Gateway In block可以完成從Simulink資料型別到FPGA資料型別的轉換:

藉助於此功能,在Simulink中搭建模擬模型,外部訊號可以傳入FPGA系統,方便的進行模擬測試。資料型別轉換勢必會牽扯到量化和溢位的問題,Gateway In block也對此做了相關支援,具體可參考引數設定小節。

7.2.2 block特性

除了資料型別轉換功能外,Gateway In block還具有如下特性功能:

- 定義了FPGA設計中的輸入埠,修改block名稱即可修改HDL埠訊號名稱;

- 使用System Generator生成testbench時,軟體會將輸入到Gateway In

block的Simulink模擬訊號按照設定的資料格式轉換並存儲到dat檔案中,在testbench中呼叫(具體可參考本系列上一篇博文)。

7.2.3 引數設定

(1).在Output Type和Arithmetic type中可以設定轉換後輸出資料的格式:

- Boolean:布林邏輯值,在HDL模型中對應單位元訊號。

- Fixed-point:定點數,包括“Signed(2’s comp)”帶符號數二進位制補碼和“Unsigned”無符號數兩種。

- Floating-point:浮點數,Floating-point

Precision可以設定資料為單精度(Single)、雙精度(Double)或自定義的浮點數格式(Custom,自行規定指數與尾數位寬)。

(2).用有限位寬表示Simulink中的資料型別,必然會產生量化誤差。在Quantization中可以選擇資料的量化方式:

- Truncate:直接捨棄不需要的低位。

- Round(unbiased:+/-Inf):以四捨五入的方式量化。

(3).資料轉換過程中還可能會出現溢位(設定的資料格式無法表示Simulink中的值),Overflow中可以設定不同的處理方式:

- Wrap:捨棄掉需要表示的值的高位。

- Saturate:溢位的數轉換為(所設定的資料格式能表達的)最大值或最小值。

- Flag as error:溢位時Simulink會報錯(這個選項只在Simulink模擬時有效,在匯出到FPGA時仍當作wrap處理)。

這裡可以設定Gateway In轉換到FPGA設計後的介面型別:“None”表示作為HDL設計的輸入埠;“AXI4-Lite”表示會被當作AXI4-Lite匯流排(目前不會用到,相關配置也暫時不做介紹)。

IOB timing constraint設定該埠的時序約束:“None”表示不作約束;“Data rate”會將System Generator block中的系統時鐘週期設定作為IO時鐘約束。

如果System Generator的設計中,Gateway In恰好對應於FPGA硬體設計中的某個管腳,可以選中“Specify IOB location constraints”,根據提示完成管腳位置與IO電平標準的設定。

7.3 Gateway Out block

7.3.1 block特性

與上一個block相反,Gateway Out block是完成從FPGA資料型別到Simulink資料型別的轉換。其具有如下特性:

定義了FPGA設計中的輸出埠,修改block名稱即可修改HDL埠訊號名稱。Gateway Out還可以只作為測試埠,此時只是為了觀察DSP系統內部,不會匯出到FPGA設計中。

使用System Generator生成testbench時,軟體會把從Gateway Out block輸出的Simulink模擬訊號儲存到dat檔案中,在testbench中呼叫來幫助設計中檢查設計是否符合預期。

7.3.2 引數設定

當System Generator設計的DSP系統後續還接入了其它Simulink模擬模組時(即System Generator僅作為Simulink模擬的一個子系統),需要選中“Propagate data type to output”,將FPGA資料型別轉換為相應的Simulink資料型別。

當選中“Translate into output port”時,該block將會作為FPGA設計的輸出埠;如果沒有選中,則該block會被視作為了觀察DSP系統內部訊號的測試埠,同時該block在Simulink中顯示為灰色,如下圖:

“Implementation”標籤下的設定與上一個block基本相同,不再贅述。

8、設計優化與匯入MATLAB變數

8.1 優化設計

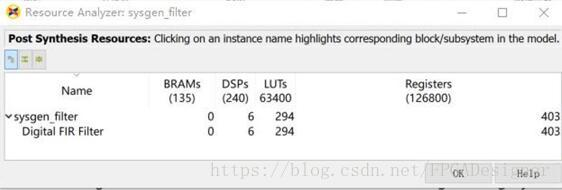

在第4篇中我們進行了設計的資源分析,結果如下:

該設計使用了6個DSP單元,這是因為該FIR濾波器係數有11個,且具有對稱性,因此需要使用6個乘法器並行運算。開啟FDATool,點選上方的“Filter Coefficients”按鈕,可檢視濾波器係數:

System Generator中FPGA時鐘設定為20MHz;Gateway In block的取樣率也為20MHz。這樣每個時鐘都要處理一個數據,因此在實現濾波器時採用了並行結構,佔用了6個乘法器。

我們可以設定過取樣模式來優化設計的資源使用率。在System Generator block中將FPGA clock period設定為8.33ns(120Mhz);Simulink system period設定為1/120e6(120MHz);Gateway In的取樣率比便。這樣每6個時鐘處理一個數據,期望所有的乘法操作能共用一個乘法器。

點選Generate匯出設計,此時Simulink會提示一個警告:

主要提示我們取樣率和時鐘的設定,本設計是故意採用這種設定方式的,因此不用在意這個警告。執行結束後,生成資源分析報告:

看到DSP單元只使用了一個,其它資源也節省了超過一半,符合預期。總而言之,在進行System Generator設計時,要綜合考慮設計指標和硬體實際情況來對設計進行鍼對性優化。

8.2 匯入MATLAB變數

Simulink已經提供了足夠強大的功能,但有些設計還是需要在MATLAB中進行(比如考察位寬對資料量化的影響)。System Generator提供了該特性:可以將MATLAB的workspace中的變數直接用於block引數配置。

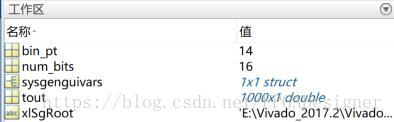

假設在MATLAB中已經確定某一資料的最佳位寬,workspace如下:

開啟Gateway In block(或其它需要配置該值的block),在編輯框裡直接輸入workspace中的變數名稱即可:

所有的block都支援該特性。

9、選擇最佳資料型別

目前,還有些問題需要解決:

- 如何選擇一個最合適的資料型別(以最少資源達到效能需求)?

- 如何選擇系統的輸出位寬(保證訊號不失真)?

傳統的HDL模型設計方法中,博主通常會用MATLAB進行模擬,確認位寬對資料量化的影響;或在Vivado中模擬,擷取合適的濾波器輸出位數。System Generator提供的相關特性可以大大簡化該流程,本文將對此做介紹。

9.1 本設計使用到的block

Xilinx block

- Convert(->Basic Elements):資料格式轉換

- Reinterpret(->Basic Elements):資料格式轉換

其它block

- Digital Filter Design(DSP System Toolbox->Filtering->Filter

Implementations):設計數字濾波器

這裡給出了設計中用到的所有block在庫中的路徑,後文不再提及(前文用過的block沒有給出;同一block會包含在多個庫中,為了尋找方便這裡只列出一個路徑)。

9.2 FPGA設計與理想情況對比

雖然在第2篇的設計中觀察到輸出訊號的頻譜圖確實符合設計要求,但由於經過資料轉換,資料型別、位寬等問題都會影響到計算精度,我們很難評估該結果與理想情況的偏差。

Simulink環境可近似為理想環境,因此我們將System Generator濾波結果與Simulink的濾波結果作對比。新增Digital Filter Design到model中,該block的配置介面與FDATool工具完全相同,對輸入訊號進行濾波。此時model如下:

將Digital Filter Design與Digital FIR Filter的濾波器引數設定為完全相同(20Mhz取樣、1.5MHz通帶截止、8.5MHz阻帶截止、0.01dB通帶衰減、100dB阻帶衰減)。執行,理想情況(左)與System Generator的輸出頻譜對比如下:

可以看到System Generator設計的濾波器,由於資料格式、位寬的影響,與理想情況下的頻譜結果並不完全相同。對於設計者而言,需要考慮的就是這種差異是否可以接受,即是否會影響到實際的系統性能。

9.3 不同字長定點資料的對比

如果System Generator和理想情況之間的差異不能接受,就該考慮修改設計。FPGA設計可以考慮使用定點資料型別(Fixed-point)或浮點資料型別(Floating-point),但後者消耗的資源幾乎是前者的十幾倍甚至更多,設計中通常都採用定點資料格式。

在System Generator再新增一組濾波器設計(可以複製貼上),將Gateway In的資料格式設定為32-30Bits定點(32表示整體位寬,30表示小數部分位寬),與原來的16-14Bits定點資料格式作對比。此時的model如下:

如果執行後想觀察整個model中的資料型別變化,可以在System Generator的General->Block icon display中選擇“Input data types”或“Output data types”。執行完成後相關資訊會顯示在block上。

Fixed_32_30(右)與Fixed_16_14(左)的輸出頻譜對比如下:

可以看到提高了定點數的位寬後,計算精度明顯提高,輸出訊號頻譜與理想情況的頻譜已經幾乎相同。匯出設計到FPGA,執行資源分析:

可以看到增加了資料位寬後,系統使用的FPGA資源幾乎增加了一倍(FIR single與FIR fixed相比)。設計者需要在資源和效能之間衡量,選擇最合理的設計。用類似的方法也可以比較不同濾波器係數位寬對FIR濾波系統的影響。

9.4 系統輸出位寬選擇

當使用Fixed_16_14格式時,FIR濾波器的輸出位寬系統會自動設定為Fixed_36_33,這是全精度輸出結果。而在FPGA設計中我們經常需要截位,否則位寬在整個系統中不斷積累,大大增加資源的消耗。如何確定擷取的位數呢?

System Generator中有兩個與此相關的block:Convert和Reinterpret,都可以進行資料的轉換。Convert可以實現不同資料型別、不同位寬之間的轉換,且可以設定量化和溢位的處理方式;Reinterpret可以實現資料型別之間的轉換,還可以重新定義輸出資料小數點的位置。

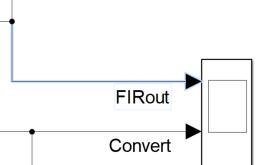

新增這兩個block到model中,按下圖連線:

使用Convert將FIR輸出的Fixed_36_33資料轉換為Fixed_16_13資料;使用Reinterpret將小數點重定位在第31bit(即資料放大4倍),具體配置可參考本系列第8篇。執行模擬:

從頻譜圖對比可以看出,經過Convert轉換後,輸出訊號的頻譜情況進一步惡化,設計者需要考慮截位是否會影響到系統性能。

使用Scope分別觀察FIR輸出、Convert轉換後、Reinterpret轉換後的訊號:

可以看到Fixed_36_33和Fixed_16_13兩種資料格式的訊號波形幾乎完全相同(第一和第二個波形)。Reinterpret由於將小數點從33bit重新定義到了31bit,相當於放大了4倍,輸出訊號的範圍擴充套件為-4~4(Sine Wave block輸出訊號的幅度設定為1)。

將用作測試埠的Gateway設定為不作為output,匯出到FPGA中後,濾波器輸出位寬只有16Bits(第2篇沒有截位的設計為輸出36Bits)。

9.5 Scope使用技巧

在第2篇中已經介紹瞭如何用Scope觀察多路訊號,本文不再贅述。這裡在介紹兩個設計技巧:

設定顯示範圍

在View->Configuration Properites:Scope->Display中可以設定波形顯示範圍。Active display選擇訊號通道,設定Minimum和Maximum。點選Apply即可應用該設定。

設定訊號名稱

在Simulink模型中,雙擊接入Scope的連線,即可出現一個編輯框(同時線變為藍色),輸入的名稱將作為Scope中波形視窗的title(也可以在上圖中的“Title”編輯框中設定)。

10、Reinterpret和Convert詳解

本文將對其中使用到的Reinterpret和Convert模組進行詳細介紹。

10.1 模組功能概述

- 資料轉換,資料型別、位寬等問題都會影響到計算精度,對於設計者而言,需要考慮的就是相關影響是否可以接受,即是否會影響到實際的系統性能。FPGA設計中還經常需要截位,否則位寬在整個系統中不斷積累,大大增加資源的消耗。

- 資料型別的轉換和截位是FPGA系統設計的重要內容,博主在《FPGA數字訊號處理》系列的很多設計中都有詳細討論。而在System Generator設計中,完成這項任務的便是Reinterpret和Convert模組。

- 資料型別轉換模組在匯出到FPGA設計中(定點與浮點之間的轉換、浮點與浮點之間的轉換),會使用Floating-Point IP核實現,具體可參考《FPGA數字訊號處理》,本系列不詳細介紹。

10.2 Reinterpret block

10.2.1 block特性

這個block可以完成以下資料轉換功能:

- 將無符號數轉換為帶符號數;

- 將帶符號數轉換為無符號數;

- 通過重新規定小數點位置來定義資料範圍。

需要注意的是,“轉換”在這個block中的含義更接近於其英文直譯“重新解釋”。事實上,資料在經過該block後,其位寬與每一位的值都沒有發生任何改變,變化的只有其所表示的“意義”。正如博主在《FPGA數字訊號處理》系列中強調的一樣,一個二進位制數是無符號數還是帶符號數、小數點在哪一位僅僅取決於設計者如何規定和看待它。而Reinterpret改變的便是這種“規定和看待”方式。

比如,“1100”這個數,當視作UFix_4_0(無符號定點數、4Bits位寬、小數部分0bit)時,其值為12;當視作Fix_4_2(帶符號定點數、4Bits位寬、小數部分2Bits)時,其值為-1。因為reinterpret實現的只是一種意義上的轉換,因此其在轉換為FPGA設計後,不會消耗任何資源。

既然reinterpret的輸出和輸入完全相同,那麼加入此模組有什麼作用?

- 從FPGA設計轉換到Simulink環境中時會按設定的“意義”解析資料格式;

- 完成不同格式資料之間的的拼接。

10.2.2 引數設定

(1).選中“Force Arithmetic Type”後,輸出資料格式的“意義”將轉換為(沒有選中,則輸出與輸入的表徵意義相同):無符號數(Unsigned)、帶符號數二進位制補碼(Signed(2’s comp))、浮點數(Floating-point)。

(2).選中“Force Binary Point”後,可以重新規定輸出資料的小數點位置。比如設定為31時,表明資料中的低31Bits為小數部分。

10.3 Convert block

10.3.1 block特性

該block不僅可以完成資料型別的轉換,還具有如下特性:

- 重新設定資料的量化、溢位方式;

- 重新設定定點數格式(進行資料截位)。

10.3.2 引數設定

其中大部分引數設定方法與Gateway In模組的設定完全相同,具體可參考本系列第5篇。這裡只講述兩者不同的地方。

(1).Convert模組的量化方式可以配置為“Round(unbiased: even values)”,這是針對“四捨五入”量化方式的缺點所作的改進:

- 傳統的四捨五入所有的中間值(如1.5、2.5)都會向更大的值量化,即不是完全對稱的,這樣會導致一組資料量化後平均值高於量化前的平均值。

- unbiased: even

values在處理中間值時會向更接近的偶數量化。比如1.5會量化為2;2.5仍然會量化為2(因為二者最接近的偶數都是2)。這樣量化規則在整體上會呈現出對稱性。

(2).選中“Provide enable port”後,block會增加一個en使能管腳,只有當使能有效時convert block才會執行資料轉換功能,否則將保持當前狀態不變。

(3).Latency設定了Convert輸出資料要經過多少個取樣時鐘週期的延時。注意不要混淆“取樣時鐘週期”和“FPGA時鐘週期”的概念,在過取樣系統中,一個取樣時鐘週期可能等於多個FPGA時鐘週期。

前文提到Convert在匯出到FPGA中時會以Floating-Point IP核的方式實現,“Implementation”標籤下可以設定Latency在FPGA中的實現方式:

●選中“Pipeline for maximum performance”時,Latency以流水線的方式實現,即在計算過程中增加中間級暫存器,以更多的資源實現更快的計算速度和更大的資料吞吐量。

●未選中“Pipeline for maximum performance”時,Latency以在IP核末尾增加一級移位暫存器的方式實現,這樣只是單純的實現了延時功能。