System Generator從入門到放棄(二)-Digital Filter

System Generator從入門到放棄(二)-Digital Filter

文章目錄

- System Generator從入門到放棄(二)-Digital Filter

- 一、Digital Filter

- 1、簡介

- 2、產生正弦訊號

- 3、數字濾波器的設計

- 4、FDATool block的使用

- 5、生成說明文件與testbench

- 6、資源分析與時序分析

System Generator是Xilinx公司進行數字訊號處理開發的一種設計工具,它通過將Xilinx開發的一些模組嵌入到Simulink的庫中,可以在Simulink中進行定點模擬,可以設定定點訊號的型別,這樣就可以比較定點模擬與浮點模擬的區別。並且可以生成HDL檔案,或者網表,可以在ISE中進行呼叫。或者直接生成位元流下載檔案。能夠加快DSP系統的開發進度。

一、Digital Filter

1、簡介

數字濾波器的功能是對輸入離散訊號的數字程式碼進行運算處理,以達到改變訊號頻譜的目的。

數字濾波一般分為時域濾波和頻域濾波。頻域濾波是將時域變換到頻域,對相應頻率做調整,然後反變換到時域,拋開FFT的話過程相對簡單。在這裡我們主要說時域濾波。

時域濾波器分為無限脈衝響應IIR和有限脈衝響應FIR兩種。IIR濾波器的優點是可以用較低的階數(相比同樣指標的FIR濾波器)實現濾波器。缺點一:不是線性相位,只能用於對相位資訊不敏感的訊號(如音訊訊號)。缺點二:有可能是不穩定的。在設計的過程中為了保持穩定性和因果性,要求z變換所有的極點都必須位於單位圓內。但即使是這樣,也可能由於量化舍入等因素引起的誤差最終導致IIR濾波器不穩定。FIR濾波器的優點是可以設計成具有線性相位的,並且是穩定的(FIR濾波器除原點處外沒有極點),缺點是階數高,也就是說計算量大。

具體介紹大家可以查閱相關資料。

2、產生正弦訊號

2.1 本部分設計使用到的block

Xilinx block

- 無

其它block

- Sin Wave(Simulink->Sources):生成正弦波

- Add(Simulink->Math Operations):加法器

- Scope(Simulink->Commonly Used Blocks):示波器

在庫中在庫中找到Sine Wave、add、scope,分別新增帶哦model中,如下:

新增完後如下:

修改相關屬性:

雙擊Sine Wave,可以設定正弦波的幅度、電平偏置、頻率、初相、取樣時間等資訊。這裡只需要將頻率分別設定為1MHz(2pi1e6)和9MHz(2pi9e6)。

雙擊Add,“List of signs”設定加法器的輸入埠,“++”表示兩個輸入相加(“±”則表示A-B)。

雙擊開啟示波器視窗,在View->Configuration Properties:Scope中(或者如下圖方式進行設定),將Number of input ports設定為3(觀察3路訊號);點選Layout,選擇3*1排列方式(每路訊號分開顯示):

連線,結果如下。 將Simulink模擬時間設定為0.00001(時間太長會導致模擬很慢),點選執行,Simulink視窗的右小角可以觀察到執行狀態。執行結束後開啟Scope:

第一個為1Mhz訊號,第三個為9MHz訊號,中間為兩路訊號疊加。接下來設計一個LPF濾除掉9MHz頻率分量。

PS:雙擊Scope可能看到的波形如下,是三路訊號混合在了一起,想要分開三路進行檢視,View->Layout,設定成三行模式。

最終的結果如下,第一個為1Mhz訊號,第三個為9MHz訊號,中間為兩路訊號疊加。接下來設計一個LPF濾除掉9MHz頻率分量。

3、數字濾波器的設計

3.1 本部分設計使用到的block

Xilinx block

- Digital FIR Filter(->DSP):數字濾波器

- Gateway In(->Basic Elements):資料輸入

- Gateway Out(->Basic Elements):資料輸出

- System Generator(->Basic Elements):系統管理

- FDATool(->DSP):濾波器設計

其它block

- Sin Wave(Simulink->Sources):生成正弦波

- Add(Simulink->Math Operations):加法器

- Scope(Simulink->Commonly Used Blocks):示波器

- Zero-Order Hold(Simulink->Discrete):零階保持器

- Spectrum Analyzer(DSP System Toolbox->Sinks):頻譜分析儀

3.2 數字濾波器設計

我們知道,Simulink中的模擬模型為連續時間系統,資料格式多種多樣;而FPGA中為離散時間系統,資料必須用一定的位數進行量化。兩者之間必須要進行從連續到離散的轉換、資料格式的轉換,否則無法進行正確的FPGA設計。Xilinx Blockset中提供了相應的解決方案。

新增一個Gateway In和一個Gateway Out模組到model中,再新增一個Digital FIR Filter模組。按照加法器輸出->Gateway In->Digital FIR Filter->Gateway Out的順序依次連線。

新增如下block到model並按圖中方式進行連線。

雙擊開啟Gateway In模組的屬性視窗:

這個模組可以Simulink到FPGA之間的資料轉換。將Sample period設定為“1/20e6”(20MHz取樣率),完成連續時間到離散時間的轉換;設定Out Type完成資料格式的轉換。這裡保持為預設的二進位制帶符號數補碼、定點數的設定。Quantization中可以設定量化方式為Truncate(截斷)或者round(四捨五入)。

Gateway In的設定會自動傳遞到Gateway In和Gateway Out之間的整個系統中,因此不需要再設定其它模組的取樣率與資料格式。

Digital FIR Filter設定

頻率引數

- Units = MHz

- Fs = 20

- Fpass = 1.5

- Fstop = 8.5

Magnitude Specifications

- Units = dB

- Apass = 0.01

- Astop = 100

兩種方式,其中第一種方式,在其他模組沒有FDATOOL工具時,需要使用第二種方式。

第一種方式

雙擊Digital FIR Filter: 選中“Use FDA Tool as coefficient source”,點選“FDA Tool”按鈕,會彈出FDATOOL視窗,設定取樣率為20Mhz,通帶截止頻率1.5MHz,阻帶截止頻率8.5Mhz,通帶衰減0.01dB,阻帶衰減100dB,點選“Design Filter”設計後退出。

第二種方式

第二種方式是使用FDATool,這部分會在後面介紹。

3.3 FPGA系統配置

以上僅僅是完成了數字濾波器的設計,但是仍然沒有建立起模型與FPGA之間的實質聯絡。新增System Generator模組到model中,這個block便是配置與FPGA相關的系統引數。這個block的配置會應用到Gateway In和Gateway Out之間的所有模組中。雙擊開啟,切換到Clock標籤:

- a. Specify an FPGA clock Period of 50 ns (1/20 MHz).

- b. Specify a Simulink system period of 1/20e6 seconds.

- c. From the Perform analysis menu, select Post Synthesis and from

Analyzer type menu select

FPGA clock period設定為50ns,Simulink system period設定為1/20e6(都是20Mhz)。Perfor analysis設定為Post Sythesis,Analyzer type設定為Resource,在系統綜合後會進行資源使用情況的分析。

3.3 開始模擬

使用Simulink完成FPGA中的DSP系統設計,最大的好處就是模擬極其方便(包括後面文章會用到的ModelSim協同模擬、硬體協同模擬等特性)。

新增一個Scope觀察Gateway Out輸出的波形(濾波後波形),再新增兩個Spectrum Analyzer觀察濾波前後的訊號頻譜。Spectrum Analyzer這個block必須輸入離散的資料,因此在加法器輸出後需要經過一個零階保持器Zero-Order Hold,轉換為離散資料後再輸入到Spectrum Analyzer中。零階保持器的取樣率設定為1/20e6(20Mhz)。

系統的整體連線框圖如下:

注意,雖然Gateway In轉換後的資料也是離散的,但是Spectrum Analyzer不能接入到這裡,否則會出現錯誤。Gateway In和Gateway Out之間只能連線其它Xilinx Blockset中的模組。

將模擬時間設定為0.0005(Spectrum Analyzer必須有足夠多的取樣資料才能計算出頻譜),輸出訊號的波形如下所示,經過濾波後僅剩下1MHz的單頻分量,且資料為離散值。

FIR濾波器前後的頻譜:

可以看到經過濾波後,9Mhz的頻率分量有大約100dB的衰減(頻譜呈對稱性),設計符合預期。

3.3 將設計匯出到FPGA

模擬驗證功能正確後,需要將設計匯出到FPGA中,這個步驟仍然要藉助System Generator這個block。雙擊開啟,切換到Compilation標籤下,這裡可以設定使用的開發板(Board,只能選擇Xilinx官方開發板)、FPGA晶片(Part),也可以設定匯出設計的硬體描述語言(Verilog或VHDL)。點選“Generate”,System Generator會將Gateway In和Gateway Out之間的模組匯出到FPGA中。執行結束後,根據前面的設定,彈出了資源分析報告:

在slx同文件夾下,生成netlist資料夾。其中sysgen子資料夾包含了匯出的Verilog或VHDL設計檔案;ip子資料夾是設計匯出的IP核形式;ip_catalog子資料夾包含一個呼叫該IP核的Vivado的示例工程。

3.3 開啟Vivado示例工程

在ip_catalog資料夾下開啟Vivado工程,其中頂層檔案如下:

//Copyright 1986-2017 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2017.4 (win64) Build 2086221 Fri Dec 15 20:55:39 MST 2017

//Date : Sun Nov 4 02:06:37 2018

//Host : LAPTOP-8E6RLG3I running 64-bit major release (build 9200)

//Command : generate_target xilinx_lab1_bd.bd

//Design : xilinx_lab1_bd

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 ps

(* CORE_GENERATION_INFO = "xilinx_lab1_bd,IP_Integrator,{x_ipVendor=xilinx.com,x_ipLibrary=BlockDiagram,x_ipName=xilinx_lab1_bd,x_ipVersion=1.00.a,x_ipLanguage=VERILOG,numBlks=1,numReposBlks=1,numNonXlnxBlks=1,numHierBlks=0,maxHierDepth=0,numSysgenBlks=1,numHlsBlks=0,numHdlrefBlks=0,numPkgbdBlks=0,bdsource=SYSGEN,synth_mode=OOC_per_IP}" *) (* HW_HANDOFF = "xilinx_lab1_bd.hwdef" *)

module xilinx_lab1_bd

(clk,

gateway_in,

gateway_out);

(* X_INTERFACE_INFO = "xilinx.com:signal:clock:1.0 CLK.CLK CLK" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME CLK.CLK, CLK_DOMAIN xilinx_lab1_bd_clk, FREQ_HZ 100000000, PHASE 0.000" *) input clk;

(* X_INTERFACE_INFO = "xilinx.com:signal:data:1.0 DATA.GATEWAY_IN DATA" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME DATA.GATEWAY_IN, LAYERED_METADATA undef" *) input [15:0]gateway_in;

(* X_INTERFACE_INFO = "xilinx.com:signal:data:1.0 DATA.GATEWAY_OUT DATA" *) (* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME DATA.GATEWAY_OUT, LAYERED_METADATA xilinx.com:interface:datatypes:1.0 {DATA {datatype {name {attribs {resolve_type immediate dependency {} format string minimum {} maximum {}} value {}} bitwidth {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 37} bitoffset {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 0} real {fixed {fractwidth {attribs {resolve_type immediate dependency {} format long minimum {} maximum {}} value 33} signed {attribs {resolve_type immediate dependency {} format bool minimum {} maximum {}} value true}}}}}}" *) output [36:0]gateway_out;

wire clk_1;

wire [15:0]gateway_in_1;

wire [36:0]xilinx_lab1_1_gateway_out;

assign clk_1 = clk;

assign gateway_in_1 = gateway_in[15:0];

assign gateway_out[36:0] = xilinx_lab1_1_gateway_out;

xilinx_lab1_bd_xilinx_lab1_1_0 xilinx_lab1_1

(.clk(clk_1),

.gateway_in(gateway_in_1),

.gateway_out(xilinx_lab1_1_gateway_out));

endmodule

sysgen_filter_bd是呼叫System Generator匯出的IP核的子模組。16Bits輸入資料經過濾波後得到36Bits的輸出結果。執行RTL ANALYSIS,開啟RTL檢視,找到最底層:

可以看到其本質上仍然是呼叫了FIR Compiler IP核來實現數字濾波,只不過我們是在Simulink中完成的設計。在其它工程中可以像示例工程一樣呼叫這個System Generator匯出的IP核,來完成特定的DSP系統功能。

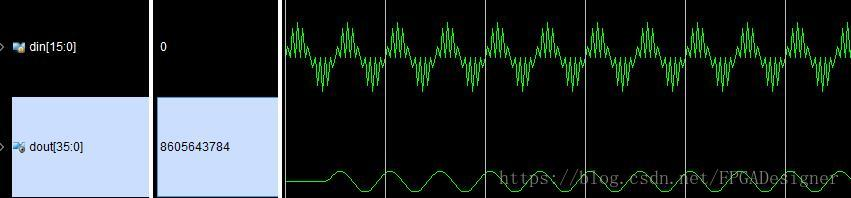

理論上經過Simulink中的模擬,已經可以確定設計的正確性。但這是使用System Generator完成的第一個實驗,本文仍然在Vivado中進行一次模擬,增強使用者對System Generator設計的信心。使用MATLAB產生一個1MHz+9Mhz的正弦疊加訊號,匯入到TXT檔案中。編寫testbench讀取txt檔案,對訊號進行濾波。Vivado中的模擬結果如下圖所示:

可以看到經過濾波後,只剩下1Mhz的單頻訊號,與Simulink中的模擬結果完全一致。

總而言之,從這個實驗出發,博主認為在System Generator中完成DSP系統設計與直接在Vivado環境下進行DSP系統設計相比,有兩個優點:

- 更強大、更方便的模擬環境;

- 系統級設計角度,無需關心RTL設計細節以及一些IP核的具體使用方法。

4、FDATool block的使用

前文中我們在Digital FIR Filter block的配置介面直接呼叫FDATool工具完成FIR濾波器的設計。但是有一些濾波器block,如2n-tap MAC FIR Filter,並沒有提供這樣一個介面。Xilinx Blockset中單獨提供了一個FDATool block,可以提供更廣泛的使用。

新增FDATool block到model中,配置完成後點選“Design Filter”。其它模組呼叫這個FDATool設計的濾波器可以藉助兩個函式:

- xlfda_numerator(‘FDATool’):提取濾波器係數的分子

- xlfda_denominator(‘FDATool’):提取濾波器係數的分母

對於FIR濾波器而言,分母為1,只提取分子即可。如下圖所示:

所有濾波器block的係數都可以用這種方式設定。

5、生成說明文件與testbench

5.1 生成說明文件

本文在上一篇設計的數字濾波器模型基礎上進行修改。開啟System Generator這個block,在Compilation標籤下:

選中“Create interface document”,在點選Generate匯出設計後,在netlist/sysgen資料夾下會生成一個HTM檔案。用瀏覽器開啟如下:

5.2 生成testbench

在System Generator block的Compilation標籤下選中“Create testbench”,如第一幅圖所示。在點選Generate匯出設計時,軟體會根據選擇的硬體描述語言生成對應的testbench(在netlist/sysgen資料夾下):

●“Verilog“對應”name_tb.v“檔案

●“VHDL“對應”name_tb.vhd“檔案

name為simulink模型的名字,我這裡為“sxilinx_lab1_tb“。在生成的Vivado示例工程中會自動新增這個testbench檔案:

在這個testbench中包含4個子模組:時鐘生成模組xlclk、測試資料輸入模組xltbsource、模組資料輸出模組xltbsink和IP核設計檔案sysgen_filter_0。最後在頂層模組中呼叫4個子模組,組成一個完整的測試平臺(在“Testbench編寫指南系列”中會解析這種testbench編寫方式)。

直接執行模擬,Vivado中模擬結果如下所示:

模擬結果與上一部分完全一致。這是因為System Generator工具在生成testbench檔案時將simulink環境中接入到Gateway In block的資料儲存到dat檔案中,在testbench中呼叫。而我們自己編寫testbench時需要設計M檔案產生訊號,再用HDL語言設計模擬過程。可見System Generator的便利與強大。

6、資源分析與時序分析

6.1 檢視分析結果

這部分繼續在上面設計的數字濾波器模型基礎上執行分析。System Generator集成了時序分析和資源分析功能,以確保在simulink中設計的DSP系統匯出到FPGA環境中能夠正確執行。其本質上仍然是在後臺呼叫Vivado進行分析,System Generator只是讀取了分析結果並顯示出來。

設計完成並且Simulink執行完畢後,開啟System Generator這個block,切換到Clock標籤下:

Perform analysis中可以設定

- None:不進行分析;

- Post Synthesis:綜合後進行分析;

- Post Implementation:實現後進行分析。

Analyzer type中可以設定

- “Resource”(進行資源分析)

- “Timing”(進行時序分析)

注意在Perform analysis設定好,並且匯出設計到FPGA後,可以切換Analyzer type,並且點選右邊的“Launch”檢視兩種報告。但修改設計和修改Perform analysis引數後必須重新執行才能生成最新的報告。

綜合後和實現後的資源分析和時序分析分別如下。時序報告中可以看到每一條時鐘路徑的情況(本設計中只有一條);資源報告中可以看到每一個模組的資源消耗(本設計只有一個模組)。可以看到綜合後與實現後的資源消耗情況、時序情況有些差異:

6.2 時序分析

System Generator整合的靜態時序分析功能提供瞭如下特性:

- 點選每一列的指標名稱,可以選擇升序/降序排列;

- 時序不滿足時,相應的路徑Slack值為負數,且顯示為紅色;

- 交叉定位功能:時序報告中選中某一路徑,Simulink模型中對應的部分會高亮顯示(時序滿足為綠色;不滿足為紅色),這可以幫助設計者更快的找到和修改時序錯誤。

如下圖:

- 時序不滿足時,可以考慮修改設計(如增加一些單元的Latency,以資源換速度),或者更換綜合策略/實現策略。

在System Generator block的Compilation標籤下可以設定“Synthesis strategy”和“Implementation strategy”。列表中有幾種Vivado提供的策略,也可以在Vivado中新增好使用者自定義的策略,在System Generator中呼叫。

6.3 資源分析

System Generator整合的資源分析功能提供瞭如下特性:

- 點選每一列的指標名稱,可以選擇升序/降序排列;

- BRAMs(包括RAMB36E、FIFO36E、RAMB18E、FIFO18E0資源);DSPs(包括DSP48E、DSP48E1、DSP48E2資源);Registers(包括暫存器和觸發器,以FD和LD開頭的資源);LUTs(所有的查詢表);

- 交叉定位功能:資源報告中選中某一模組,Simulink模型中對應的部分會高亮顯示(黃色),如下圖:

- 資源消耗超過FPGA晶片總資源時,可以考慮修改設計,或者更換綜合策略/實現策略。這裡與時序分析部分相同。

6.4 資時序/資源分析失敗的說明

絕大多數情況下,時序分析和資源分析都能得到正確的結果,但有時在Generate生成結束後,會提示一個Error,無法獲取結果資料。

失敗的原因一般都是如下情況:在同一目錄下有多個slx檔案,但是所有的slx檔案設定的輸出目錄都相同(比如都是預設的./netlist)。在匯出第一個slx檔案時是可以正確執行時序/資源分析的;但在匯出第二個slx檔案的設計時,就會報錯。原因便是不同的模型向同一目錄下匯出設計。在設定路徑時要注意。