System Generator從入門到放棄(六)-利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼

System Generator從入門到放棄(六)-利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼

文章目錄

- System Generator從入門到放棄(六)-利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼

- 一、利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼

- 1、簡介

- 2、利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼 流程

- 3、Vivado HLS block詳解

System Generator是Xilinx公司進行數字訊號處理開發的一種設計工具,它通過將Xilinx開發的一些模組嵌入到Simulink的庫中,可以在Simulink中進行定點模擬,可以設定定點訊號的型別,這樣就可以比較定點模擬與浮點模擬的區別。並且可以生成HDL檔案,或者網表,可以在ISE中進行呼叫。或者直接生成位元流下載檔案。能夠加快DSP系統的開發進度。

一、利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼

1、簡介

Vivado HLS是Xilinx FPGA開發套件中的一款軟體,可以使用C/C++語言進行設計,並轉換為RTL級模型。System Generator中的Vivado HLS block可以將HLS開發軟體設計的C/C++程式碼整合到Simulink環境中,利用Simulink強大的模擬特性對設計進行模擬測試。

ug948中提供的官方例程為影象的中值濾波,該設計將一副256*256大小的RGB影象,新增噪聲後提取出其中的Y通道,使用C++語言完成中值濾波。該設計將在Simulink環境下進行模擬。

本次設計的流程是利用Vivado HLS建立C/C++程式碼,Export RTL–>System Generator–>Vivado。

2、利用Vivado HLS block實現Vivado HLS呼叫C/C++程式碼 流程

2.1 Vivado HLS完成中值濾波設計

建立相關HLS中的程式,其中Source中建立MedianFilter.cpp程式,程式如下:

PS:這部分例程在官方ug948-design-files.zipLab2中找到。

MedianFilter.cpp

#include "MedianFilter.h" #define WINDOW_SIZE 3 typedef unsigned char PixelType; #define PIX_SWAP(a,b) { PixelType temp=(a);(a)=(b);(b)=temp; } #define PIX_SORT(a,b) { if ((a)>(b)) PIX_SWAP((a),(b)); } PixelType OptMedian9(PixelType * p) { PIX_SORT(p[1], p[2]) ; PIX_SORT(p[4], p[5]) ; PIX_SORT(p[7], p[8]) ; PIX_SORT(p[0], p[1]) ; PIX_SORT(p[3], p[4]) ; PIX_SORT(p[6], p[7]) ; PIX_SORT(p[1], p[2]) ; PIX_SORT(p[4], p[5]) ; PIX_SORT(p[7], p[8]) ; PIX_SORT(p[0], p[3]) ; PIX_SORT(p[5], p[8]) ; PIX_SORT(p[4], p[7]) ; PIX_SORT(p[3], p[6]) ; PIX_SORT(p[1], p[4]) ; PIX_SORT(p[2], p[5]) ; PIX_SORT(p[4], p[7]) ; PIX_SORT(p[4], p[2]) ; PIX_SORT(p[6], p[4]) ; PIX_SORT(p[4], p[2]) ; return(p[4]) ; } PixelType Mean(PixelType* buffer) { PixelType i, j, min; unsigned int sum; for (i = 0;i<9; i++) { sum+=buffer[i]; } sum/=(WINDOW_SIZE*WINDOW_SIZE); return sum; } PixelType Min(PixelType* buffer) { PixelType i, j, min; min = buffer[0]; for (i = 1;i<9; i++) { if (min>buffer[i]) min = buffer[i]; } return min; } void MedianFilter(PixelType row1, PixelType row2, PixelType row3, PixelType* V) { #pragma AP PIPELINE II=1 /* * Create a local Pixel Buffer based on WindowSize */ static PixelType pixelWindowBuffer[WINDOW_SIZE*WINDOW_SIZE]; PixelType sortBuffer[WINDOW_SIZE*WINDOW_SIZE]; /* * Each Iteration Interval Update the Pixel Buffers */ for(int i = 0;i<WINDOW_SIZE;++i) { for(int j=0;j<(WINDOW_SIZE-1);++j) { pixelWindowBuffer[WINDOW_SIZE*i + (WINDOW_SIZE-j-1)] = pixelWindowBuffer[WINDOW_SIZE*i + (WINDOW_SIZE-j-1)-1]; } } /* * Update the first Pixel of each row */ pixelWindowBuffer[0] = row1; pixelWindowBuffer[3] = row2; pixelWindowBuffer[6] = row3; for(int k = 0;k<9;++k) { sortBuffer[k] = pixelWindowBuffer[k]; } *V = OptMedian9(sortBuffer); }

MedianFilter.h

#ifndef __MEDIAN__FILTER__

#define __MEDIAN__FILTER__

void MedianFilter(unsigned char R, unsigned char G, unsigned char B, unsigned char* V);

#endif

右鍵Solution->C Synthesis->Active Solution,綜合設計原始檔。

當綜合完成時, Vivado HLS displays 將顯示this message:

- Finished C synthesis.

完成後,再右鍵Solution->Export RTL,Format Selection選擇為“System Generator for DSP”,點選OK將設計原始檔打包為System Generator可以使用的形式。

當Export RTL完成時, Vivado HLS displays 將顯示:

- Finished export RTL

2.2 將HLS設計匯入System Generator

Xilinx block

- Vivado HLS block(->Index):呼叫HLS程式碼

- System Generator(->Basic Elements):系統管理

- Gateway In(->Basic Elements):資料輸入

- Gateway Out(->Basic Elements):資料輸出

其它block

- 影象處理相關Block

- Scope(Simulink->Commonly Used Blocks):示波器

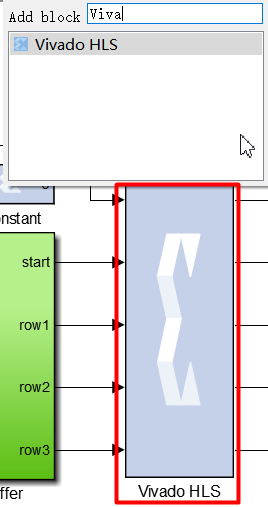

新增一個Vivado HLS block,雙擊開啟該block:

點選Browse,將路徑指定到HLS工程的Solution資料夾下。如果路徑選擇錯誤,或者HLS工程綜合或匯出失敗導致solution資料夾下沒有可用的System Generator檔案,軟體會提示錯誤。

設定完畢後,block埠也會隨之改變,部分埠名稱以ap_開頭,表示與block之間的ap_hs通訊協議。model的整體連線圖如下:

其中包含幾個子系統,各子系統及其作用如下:

- Noisy Image:匯入一副256*256的影象,轉換為一維資料,併為其新增椒鹽噪聲;

- RGB2Y:將R、G、B通道轉換為Y通道(Y=0.299R+0.587G+0.114B,可以簡化為只用兩個乘法器的形式Y=0.299(R-G)+0.114*(B-G)+G);

- LineBuffer:快取器儲存資料;

- Noisy Input Image/Filtered Image:快取資料,將一維資料轉換為二維影象顯示。

2.3 模擬測試

在Noisy Image子系統下,開啟Image From File這個block(屬於Computer Vision System Toolbox庫)。點選Browse,將路徑指向一副256256大小的彩色圖片。將模擬時間設定為256256*2,確保可以完成一次影象濾波。執行結果如下:

Use the toolbar button Up  to Parent to return to the top level

to Parent to return to the top level

儲存後,進行模擬,結果如下:

PS:執行時間比較久,要耐心等待!!

可以看到經過中值濾波後,很好地濾除了影象中的椒鹽噪聲。

3、Vivado HLS block詳解

摘自:https://blog.csdn.net/FPGADesigner/article/details/80985418

該block支援C、C++和System C三種設計原始檔。使用是首先需要在Vivado HLS開發環境下將設計原始檔打包到Solution目錄下,然後在block中指向該目錄,將設計匯入到System Generator設計中。

點選“Edit”可以開啟與該solution對應的Vivado HLS工程,允許設計者修改;修改後點選“Refresh”更新block的埠資訊。

block預設採用RTL-model進行模擬,如果HLS中包含C模擬模型,可以選中“Use C simulation model if available”,選擇C模擬模型。

當選中“Display signal types”時,輸入和輸出的資料型別會顯示在圖示上,設計者可以根據該提示設定向此block輸入的資料,如下圖:

C/C++資料型別和System Generator資料型別之間的轉換關係如下表:

在Vivado HLS中進行設計時有如下限制:

- 設計不能是純組合邏輯,綜合到RTL設計後必須包含一個時鐘和時鐘使能輸入訊號;

- 頂層模組中不能包含C/C++模板語法;

- C模擬模型與block通訊時支援ap_hs通訊協議,但不支援ap_memory和ap_bus介面。