AXI4 STREAM DATA FIFO使用

AXI4 STREAM DATA FIFO是輸入輸出介面均為AXIS介面的資料快取器,和其他fifo一樣是先進先出形式。可以在跨時鐘域的應用中用於資料緩衝,避免亞穩態出現。支援資料的分割和資料拼接。在使用該IP核之前,我們應該熟悉該IP核的各種引數設定的含義。

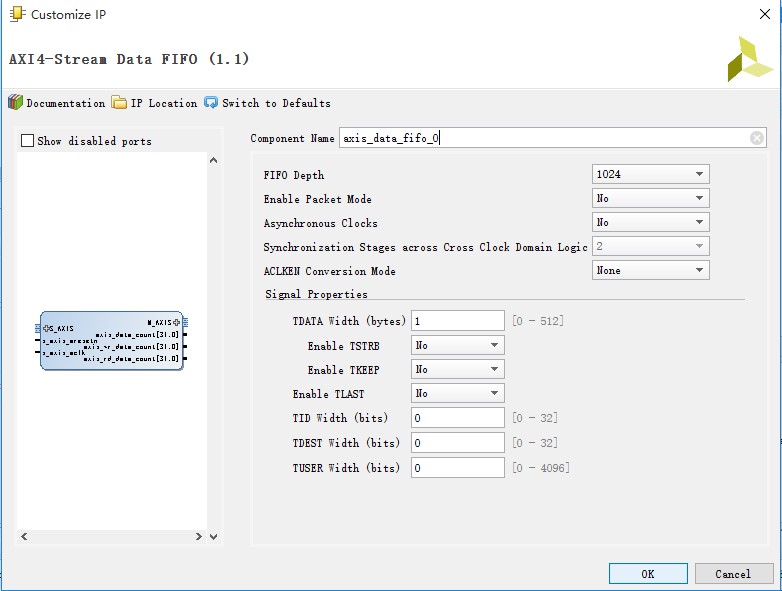

Component Name: 元件名字:該IP核生成後的模組名;

FIFO Depth: FIFO深度:該設定為指定例化FIFO的深度。當FIFO的深度為16或者32時利用基於FIFO的LUTRAM,其他深度的FIFO將利用BLOCK RAM實現。

Enable Packet Mode: 使能包模式:設定為Yes將使能包模式。此項設定需要TLAST訊號被使能。FIFO的操作在包模式下被修改為儲存傳送的資料,知道TLAST訊號被斷言(響應)。當TLAST訊號被響應或者FIFO滿了,儲存的傳送資料將被送至AXI4-Stream master interface。

Asynchronous Clocks: 非同步時鐘:如果設定了Yes,S_AXIS_ACLK和M_AXIS_ACLK被設定為與彼此非同步,該IP將在非同步模式進行操作。

Synchronization Stages across Cross Clock Domain Logic: 跨交叉時鐘域邏輯的同步階段: 當S_AXIS_ACLK和M_AXIS_ACLK是與彼此非同步的,此項引數指定了用於跨時鐘域邏輯的同步階段的階數。增加這個值可以增加設計的MTBF,但是會增加延遲時間和邏輯利用。參考the FIFO Generator Product Guide(PG075)獲得該引數的更多資訊。

ACLKEN Conversion Mode ACLKEN轉換模式: 這個下拉選項為ACLKEN訊號的轉換模式。當ACLKEN轉換執行時會消耗額外的延遲和邏輯。這個選項有: None - 這裡沒有ACLKEN訊號關聯於IP。 S AXIS Only - 一個S_AXIS_ACLKEN訊號關聯到S_AXIS_ACLK時鐘訊號和沒M_AXIS_ACLKEN訊號。 M AXIS Only - 一個M_AXIS_ACLKEN訊號關聯到M_AXIS_ACLK時鐘訊號和沒有S_AXIS_ACLKEN訊號。 S AXIS & M AXIS - 兩邊時鐘都有 ACLKEN訊號關聯到他們。

Signal Properties: 訊號特性: 當使用IP整合器是,Vivado IDE會自動計算這些引數的值。

TDATA Width(bytes): TDATA位寬(位元組為最小單位): 該引數指定了所有AXI4-Stream interfaces中的TDATA訊號的位寬,以位元組為最小單位。該引數為整數,在0到512之間。設為0將省略TDATA訊號。如果TDATA訊號被省略,TKEEP和TSTRB訊號也會被省略。介面資料的位寬按bits計算,需要乘以8。

Enable TSTRB 使能TSTRB訊號 如果設定為Yes,這個引數指定是否在所有AXI4-Stream interfaces使用可選的TSTRB訊號。這個選項只能在TDATA Width(bytes)引數大於0時才可以使能。

Enable TKEEP 使能TKEEP訊號 如果設定為Yes,這個引數指定是否在所有AXI4-Stream interfaces使用可選的TKEEP訊號。這個選項只能在TDATA Width(bytes)引數大於0時才可以使能。

Enable TLAST: 使能TLAST: 如果設定為Yes,這個引數指定是否在所有AXI4-Stream interfaces使用可選的TLAST訊號。對於TLAST訊號要重點說明,因為在使用STREAM FIFO時TLAST的作用特別的重要。對於STREAM FIFO來說,TLAST訊號的作用是指示一次傳輸資料流的最後一個數據,也指示著該資料流的結束。其會記錄下TLAST訊號的位置,及當其SLAVE介面(SFIFO的資料寫入介面)的某一個數據寫入的同時TLASET訊號也為高的話,當MASTER介面(SFIFO的資料讀出介面)讀出該資料的同時也會將TLAST訊號拉高。總結起來就是,進的資料有TLAST,該資料出的時候就會有TLAST。 TID Width(bits): TID位寬(位元為單位): 如果該引數大於0,這個引數指定是否在所有的AXI4-Stream interfaces中使用TID訊號。值大於0省略這個訊號。

TDEST Width(bits): TDEST位寬(bits): 如果該引數大於0,這個引數指定是否在所有的AXI4-Stream interfaces中使用TDEST訊號。值大於0省略這個訊號。

TUSER Width(bits): TUSER 位寬(bits): 如果該引數大於0,這個引數指定是否在所有的AXI4-Stream interfaces中使用TDEST訊號。值大於0省略這個訊號。

這裡重點說下Synchronization Stages across Cross Clock Domain Logic,這個引數的出現是由於在進行跨時鐘域操作時,即FIFO的讀寫時鐘非同步時,在讀時鐘域與寫時鐘域進行資料互動時可能會存在亞穩態,而通過在資料交換節點插入連續的暫存器進行時鐘同步,而這個引數的數值就是插入的同步暫存器的個數,或者叫做階數。階數越高,MTBF(Mean Time Between Failures,平均無故障時間)越大,則出現亞穩態的機率越小,但是同時也會增加訊號傳輸的延遲和增加額外的邏輯資源。

還有一個引數Packet Mode,當開啟整包傳送模式後,FIFO會一直檢測當前接收資料量,只有當資料量到達FIFO的深度時,即FIFO滿的時候(在實際測試中發現當STREAM FIFO滿的時候不會輸出TLAST訊號),或者是FIFO的SLAVE介面接收到TLAST訊號時,該FIFO的MASTER接口才可以輸出有效資料,及才會允許後級模組接收FIFO內資料。

在使用STREAM FIFO的應用中只應用到了TDATA、TVALID、TREADY以及TLAST訊號,所以接下來對STREAM FIFO的功能說明只要是針對只是用以上訊號的條件下的。

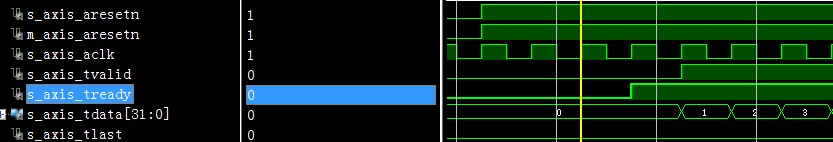

STREAM FIFO的復位訊號為低有效,當復位訊號拉高後的第三個時鐘上升沿s_axis_tready訊號會自動拉高,該fifo處於等待接收資料狀態。

當STREAM FIFO的前端有資料需要傳送時,在s_axis_tready為高時拉高s_axis_tvalid訊號,在下個時鐘上升沿,STREAM FIFO便開始收數。

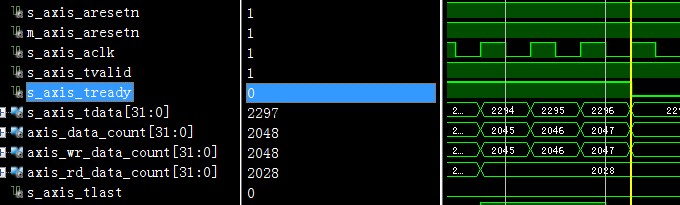

當STREAM FIFO內部的資料達到fifo的深度時,在接收進最後一個數據的同時,s_axis_tready將會變為低,告訴前級fifo已滿,不能在收資料了。其實S_axis_tready訊號相當於普通FIFO的full與empty訊號的綜合體。

對STREAM FIFO 的MASTER介面為FIFO的資料輸出介面。當STREAM FIFO接收到資料並傳到MASTER介面上時,m_axis_tvalid便會拉高,由於使用的STREAM FIFO為非同步時鐘模式,資料寫入時鐘比資料讀出時鐘要快,而讀資料計數器的重新整理是在讀資料時鐘的上升沿,所以可以從圖中看到讀資料計數器的值是跳躍上升的。當FIFO的後端將m_axis_tready拉高時,MASTER介面便會將資料送出去。

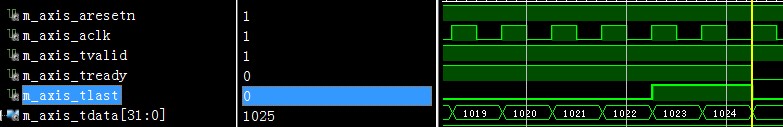

最後再來觀測下TLAST訊號:

為了說明TLAST訊號的傳輸特點,我們在SLAVE的寫入資料時在資料1023 和資料1024的時候將s_axis_tlast拉高。然後開啟MASTER介面將STREAM FIFO內部的資料讀出。

從MASTER介面的資料流可以看出,將資料1023和資料1024讀出的同時也會將m_axis_tlast訊號拉高。

最後說明一下STREAM FIFO的Packet mode包模式,開啟包模式必須是採用同步時鐘,而且TLAST訊號必須使用。

在包模式下,資料將是以包的單位,而包內資料的數量由TVALID、TREADY和TLAST訊號控制,TVALID訊號和TREADY訊號一起為包資料的開始,TLAST訊號為包資料的結束。當STREAM FIFO裡面沒有收到一包的資料時,FIFO的MASTER介面將處於關閉狀態,即m_axis_tvalid將一直保持為低。當STREAM FIFO內部資料有至少一包及以上的資料時,MASTER介面將開啟,m_axis_tvalid將會拉高,當後級將存的包資料取完之後,MASTER介面又將關閉,m_axis_tvalid將拉低,直到接收到下一包資料之後才會重新開啟。