關於video in to axi4-stream

PG043 Video In to AXI4-Stream對於video轉成AXIS的處理。

關鍵訊號

READY/VALID Handshake

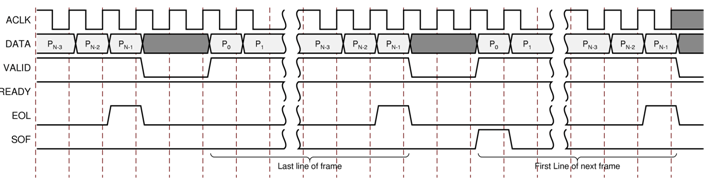

A valid transfer occurs whenever READY, VALID, ACLKEN, and ARESETn are high at the rising edge of ACLK. During valid transfers, DATA only carries active video data. Blank periods and ancillary data packets are not transferred via the AXI4-Stream Video protocol.

Driving m_axis_video_tready The m_axis_video_tready signal can be asserted before, during, or after the cycle in which the Video in to AXI4-Stream core asserted m_axis_video_tvalid. The assertion of m_axis_video_tready may be dependent on the value of m_axis_video_tvalid. A slave that can immediately accept data qualified by m_axis_video_tvalid should preassert its m_axis_video_tready signal until data is received. Alternatively, m_axis_video_tready can be registered and driven the cycle following VALID assertion. It is recommended that the AXI4-Stream slave should drive READY independently, or pre-assert READY to minimize latency.

SOF ‐ m_axis_video_tuser The SOF signal, physically transmitted over the AXI4-Stream tuser signal, marks the first pixel of a video frame. The SOF pulse is 1 valid transaction wide, and must coincide with the first pixel of the frame. SOF serves as a frame synchronization signal, which allows downstream cores to re-initialize, and detect the first pixel of a frame. The SOF signal may be asserted an arbitrary number of aclk cycles before the first pixel value is presented on tdata, as long as a tvalid is not asserted.

EOL Signal ‐ m_axis_video_tlast

The EOL signal, physically transmitted over the AXI4-Stream tlast signal, marks the last pixel of a line. The EOL pulse is 1 valid transaction wide, and must coincide with the last pixel of a scanline, as seen in Figure 2-6.

關鍵看黑體部分:

tuser在xilinx的設計中,變成了幀開始(SOF)訊號。這點很關鍵,會在VDMA中用到。

tlast在xilinx的設計中,變成了行結束(EOL)訊號。VDMA需要設定幀的解析度,EOL用於寫入畫素的統計。

關於畫素打包

在IP設定中,是允許對畫素進行打包的。

入下圖:

輸入是RGB,每個分量是8bit,選擇輸出每個分量也是8bit,每個時鐘1個畫素。可以看到m_axis_video_tdata的位寬為24。

如果每個時鐘選擇2個畫素,那m_axis_video_tdata的位寬就變成48了。

如果輸入RGB每個分量是8bit,除了8bit,輸出還可以設定成10,12,16。比如輸出位寬為10,IP會自動將8bit對映到高8位,低2位填0。。。