PYNQ上手筆記 | ⑥IP核的設計

阿新 • • 發佈:2018-12-20

1.實驗目的

用以下三種工具建立IP包:

- HDL

- Mathworks HDL Coder

- Xilinx Vivado HLS

2.HDL建立

2.1.建立一個新的專案

2.2.呼叫Create and Package IP Wizard,建立一個新的AXI-Lite從機ip

選擇Tools->Create and Package IP

編輯建立的IP

- led_controller_v1_0.v — 例項化了所有的AXI-Lite介面,在這種情況下,只有一個介面存在

- led_controller_v1_0_S00_AXI.v — 包含了處理PL外設與PS端軟體的AXI4-Lite介面功能

開啟

led_controller_v1_0_S00_AXI.v檔案,找到Users to add ports here,然後在其後新增需要的埠:

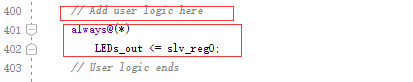

然後在檔案最後,找到Add user logic here,然後在其後新增邏輯功能程式碼:

儲存檔案,開啟led_controller_v1_0.v檔案,找到Users to add ports here,新增埠:

在頂層檔案中例化剛剛我們新增的埠,儲存檔案:

更新IP核

打包IP核

然後關閉這個工程即可,ip核建立成功。

2.3.新增ip核到Block Design中進行設計

建立Block Design:

點選Add IP,搜尋led,新增led_controllerIP:

因為LEDs_out要連線板載LED,所以點選引腳,按下ctrl+t

新增Zynq ps核,自動連線:

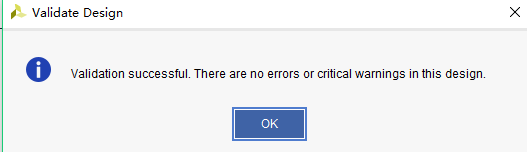

按下F6驗證設計:

建立Block Design 的HDL檔案:

新增LED引腳約束檔案:

##LEDs

#set_property -dict { PACKAGE_PIN R14 IOSTANDARD LVCMOS33 } [get_ports { LEDs_out_0[0] }]; #IO_L6N_T0_VREF_34 Sch=LEDs_out_0[0]

#set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports { LEDs_out_0[1] }]; #IO_L6P_T0_34 Sch=LEDs_out_0[1]