FPGA series # vivado之新增switch和VIO核

阿新 • • 發佈:2018-12-21

今天在之前程式碼的基礎上,把兩組置0的高位資料也通過模組跑了一遍,出來效果還可以看。順手添加了個開關,當switch置0時不經過gamma模組,置1時經過。

assign addrb_r = s_axis_gamma_tdata[23 : 16] ; assign addrb_g = s_axis_gamma_tdata[15 : 8 ] ; assign addrb_b = s_axis_gamma_tdata[7 : 0 ] ; assign m_axis_gamma_tdata_fifo_in = {8'b0,doutb_r, doutb_g, doutb_b}; assign m_axis_gamma_tdata = (switch == 1)?m_axis_gamma_tdata_fifo_out[23:0]:s_axis_gamma_tdata ; assign m_axis_gamma_tlast = (switch == 1)?m_axis_gamma_tlast_fifo : s_axis_gamma_tlast ; assign m_axis_gamma_tuser = (switch == 1)?m_axis_gamma_tuser_fifo : s_axis_gamma_tuser ; assign m_axis_gamma_tvalid = (switch == 1)?m_axis_gamma_tvalid_fifo : s_axis_gamma_tvalid; assign s_axis_gamma_tready = (switch == 1)?s_axis_gamma_tready_fifo : m_axis_gamma_tready;

這裡m_axis_gamma_tdata_fifo_in 的高八位還是要置0 是因為這個fifo的IP核只允許選擇偶數倍的byte

也就是這裡fifo的輸入輸出資料位沒有24位可選。

要提一點,assign的等式左邊必須得是wire型,reg型會報錯。這一點以前是有注意的,很久沒接觸又忘了,其實wire和reg的用法還是有點混亂,先記下,來日得好好研究研究。

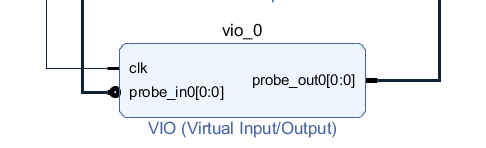

直接在block design裡新增的VIO

VIO:virtual input output;其輸出可以控制模組的輸入,輸入可以顯示模組的輸出。input可在chipscope裡當按鍵觸發。具體可以參考官方手冊

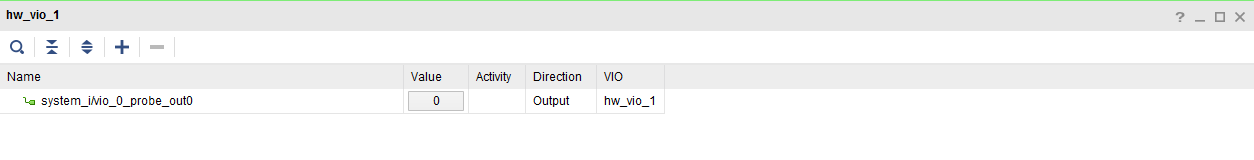

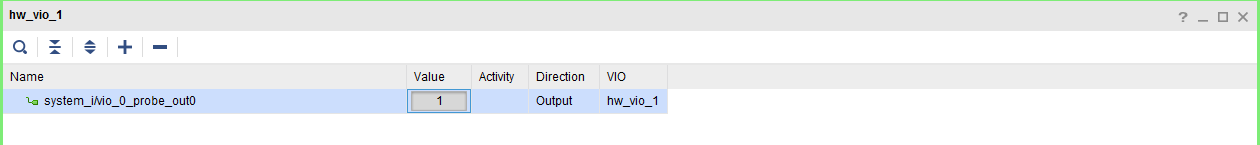

輸出接的siwtch,輸入隨手接了個訊號,只要位數對應,並無影響。vio中右鍵訊號進行設定toggle button。

value下的值即為button