MSP430F6638微控制器複習筆記

作者:BerenCamlost

適應於南理工王巨集波老師的《MSP430微控制器》課

緊急更新!!!已完結 。求關注、收藏、點贊、評論

更新啦!還是到第七章,小更新,對部分錯誤做出修改,還有增加了部分重要知識點。

參考:

- MSP430資料手冊

- 王巨集波老師的PPT

- 王巨集波老師的實驗教程

- 作者之前寫的MSP430筆記:MSP430微控制器應用技術

第一章 緒論

1.1 微控制器基礎

- 全稱:單片微型計算機(Single Chip MicroComputer)

- 它是把MPU、儲存器、I/O口、定時器/計數器、中斷系統、時鐘電路、A/D-D/A等整合在一個晶片上構成的微型計算機系統。

- 微控制器又稱:單片微控制器、嵌入式微控制器

1.2 MSP430F663x片內資源

- MSP430F663x 系列配置有一個高效能12 位ADC、比較器、兩個USCI、USB2.0、硬體乘法器、DMA、四個16 位定時器、帶有報警功能的RTC、LCD 驅動器和多達74 個I/O 。

1.3 進位制轉換

- 【注意】小數的進位制轉換

1.4 原碼、反碼、補碼的書寫

- 【注意】一般是8位補碼,有時也有16位補碼

1.5 位操作

P1OUT|=BIT1; //P1.1置1

P1OUT|=BIT0+BIT2+BIT6+BIT7; - MSP430的C編譯器不支援位定址,所以運算中儘量減少位操作。

第2章 硬體結構

2.1 MSP430 CPU 與 MSP430X CPU

- MSP430 CPU是指MSP430F1xx系列採用的16 位CPU,資料匯流排寬度16位,地址匯流排寬度16位,暫存器16位。定址空間216=64KB。

- MSP430X CPU(簡稱CPUX)是指MSP430F2xx/4xx/5xx/6xx系列採用的CPU,資料匯流排寬度16位,地址匯流排寬度20位,暫存器20位。定址空間220=1MB。CPUX的算術邏輯單元(ALU)也可以完成20位的計算。

- CPUX向下相容MSP430 CPU。

2.2 PC、SP、SR

- PC:

取完指令後CPU根據該指令的位元組數自動增量PC,因此20位的PC(R0)的值總是指向下一條要執行的指令。PC總是指向偶地址(bit0=0)。 - SP:

- 20位的堆疊指標,始終指向偶地址

- 【作用】:保護現場和恢復現場。

- 先進後出

- 堆疊分兩種:

(1)向上增長,棧底佔用較低地址,棧頂佔用較高地址:8051

(2)向下增長,棧底佔用較高地址,棧頂佔用較低地址:MSP430、AVR

(3)ARM支援兩種增長方式的堆疊。

- SR:

- 用作源或目標暫存器的16位狀態暫存器(SR,也稱為R2)只能用於通過字指令定址的暫存器模式。 定址模式的其餘組合用於支援常數發生器。

- SCG1:系統時鐘發生器1該位可用於根據器件系列啟用或禁用時鐘系統中的功能; 例如,DCO偏置啟用或禁用。

- SCG0:系統時鐘發生器0該位可用於根據器件系列啟用或禁用時鐘系統中的功能; 例如,FLL(頻率鎖定環)啟用或禁用。

- OSCOFF:關閉振盪器。 該位置1時,當LFXT1 CLK不用於MCLK或SMCLK時,它會關閉LFXT1晶體振盪器。

- CPUOFF:CPU關閉。 該位置1時,將關閉CPU。

- CPUOFF,OSCOFF,SCGO和SCG1位請求系統進入低功耗模式。

- 【例如】:關閉和開啟鎖頻環(FLL)

__bis_SR_register(SCG0); // Disable the FLL control loop

UCSCTL0 = 0x0000; // Set lowest possible DCOx, MODx

UCSCTL1 = DCORSEL_3; // Set RSELx for DCO = 4.9 MHz

UCSCTL2 = FLLD_1 + 74; // Set DCO Multiplier for 2.45MHz

// (FLL_N + 1) * FLLRef = FdcoCLKDIV

// (74 + 1) * 32768 = 2.45MHz

// Set FLL Div = fDCOCLK/2

__bic_SR_register(SCG0); // Enable the FLL control loop

//其中__bis_SR_register()函式是將SR暫存器中的相應位置1

//__bic_SR_register()函式是將SR暫存器中的相應位置0

2.3 三種系統復位

2.4 復位狀態

- 在BOR之後,初始裝置條件是:

- RST / NMI引腳配置為復位模式。

- I / O引腳切換到輸入模式。

- 狀態暫存器(SR)復位。

- 看門狗定時器在看門狗模式下上電。

第3章 中斷、時鐘與低功耗

3.1 中斷

3.1.1 各種中斷向量

| 中斷名稱(不規範) | 巨集定義 |

|---|---|

| port1口中斷 | PORT1_VECTOR |

| port2口中斷 | PORT2_VECTOR |

| 振盪器失效中斷 | 0xFFFA |

| WDT間隔定時器模式中斷 | WDT_VECTOR |

| WDT看門狗模式中斷 | 0xFFFE |

| TAxCCR0中斷中斷 | TIMER0_A0_VECTOR |

| TAIFG中斷 | TIMER0_A1_VECTOR |

| ADC12中斷 | ADC12_VECTOR |

| 串列埠中斷 | USCI_A1_VECTOR |

- 【注意】排序順序為實驗順序,不代表優先順序大小

- 中斷向量的計算

3.1.2 中斷優先順序

- 不同中斷源發出的中斷請求重要程度不同,每個中斷源對應一個優先順序,稱為中斷優先順序。

- 【作用】:多箇中斷同時發生時,決定哪個中斷被響應。

- 【注意】:

- 中斷優先順序只有在多箇中斷同時到來時才起作用,在中斷巢狀中是不考慮的

- 中斷優先順序固定不變,取決於模組在中斷向量表中的排序

3.1.3 中斷巢狀

- CPU響應某一中斷時,在開總中斷的前提下若有其他中斷髮生,CPU將中斷當前ISR,執行新的ISR。

- MSP430預設關閉中斷巢狀,即進入中斷服務函式後,預設關閉總中斷。如果想要開啟中斷巢狀需要使用者使用軟體開啟總中斷。

- 開啟和關閉總中斷例程中最常用的方式是

__bis_SR_register(GIE); // 開啟總中斷

__bic_SR_register(GIE); // 關閉總中斷

//其中__bis_SR_register()函式是將SR暫存器中的相應位置1

//__bic_SR_register()函式是將SR暫存器中的相應位置0

3.1.4 中斷服務函式

- 如果是多元中斷,可能會在終端服務函式中檢視是那種中斷置位,即用if或switch語句判斷中斷標誌位是否為1.例如:

// Timer_A1 Interrupt Vector (TAIV) handler

#pragma vector=TIMER0_A1_VECTOR

__interrupt void TIMER0_A1_ISR(void)

{

switch(__even_in_range(TA0IV,14))// __even_in_range()本徵函式,用於多源中斷的查詢。

{

case 0: break; // No interrupt

case 2: break; // CCR1 not used

case 4: break; // CCR2 not used

case 6: break; // reserved

case 8: break; // reserved

case 10: break; // reserved

case 12: break; // reserved

case 14: P4OUT ^= BIT1; // TAIFG

break;

default: break;

}

}

3.2 UCS時鐘系統

3.2.1 五種時鐘源和三種時鐘訊號

| name | function |

|---|---|

| XT1 CLK | 外部低頻,一般接32768Hz |

| VLOCLK | 內部,10K振盪器 |

| REFOCLK | 內部,32768Hz |

| DCOCLK | 內部,數控振盪器,藉助參考時鐘 |

| XT2 CLK | 外部高頻,4~32MHZ |

- 【注】DCOCLKDIV時鐘為DCOCLK分頻得到

| name | function | 預設 | 預設頻率 | 輸出方法 |

|---|---|---|---|---|

| ACLK | 用於低速外設,可由P1.0輸出 | XT1CLK | 32768Hz | P1.0 |

| MCLK | 用於CPU和系統 | DCOCLKDIV | 1048576Hz | 使用__delay_cycles();和LED檢視 |

| SMCLK | 用於高速外設,可由P3.4輸出 | DCOCLKDIV | 1048576Hz | P3.4 |

3.2.2 FLL——鎖頻環

- 計算公式:fDCOCLK ÷[D × (N + 1) ] = fFLLREFCLK ÷ n

- 【註釋】:

- D:FLLD,預設為2

- N:FLLN,預設為31

- n:FLLREFDIV, 預設為1

- fFLLREFCLK :FLL的參考時鐘,預設為XT1CLK(32768Hz)

- 所以fDCOCLK 預設為2097152Hz,fDCOCLKDIV預設為1048576Hz

3.2.3 UCS復位之後

- 由於復位的時候XT1CLK未穩定,所以ACLK和FLL的參考時鐘會自動變為REFOCLK(注意這裡是REFOCLK,和後邊WDT看門狗模式下的時鐘故障保護功能,自動變成VLOCLK相區別)

- 根據實驗情況,如果在配置ACLK和FLL之前,XT1CLK未穩定,那麼時鐘頻率會相對變低

//穩定XT1CLK和XT2CLK的程式

//1. 解鎖XT1的引腳,這是f66xx裝置獨有的

while(BAKCTL & LOCKBAK)// Unlock XT1 pins

{

BAKCTL &= ~(LOCKBAK);

}

//2. 設定XT2的引腳

P7SEL |= BIT2 + BIT3; // Port select XT2

//3. 開啟XT1, XT2

UCSCTL6 &= ~(XT1OFF + XT2OFF); // Set XT1, XT2 On

//4. 穩定XT1CLK、XT2CLK、DCOCLK

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG); // Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

//5. ACLK選擇XT1CLK、SMCLK選擇XT2CLK

UCSCTL4 |= SELA__XT1CLK + SELS__XT2CLK; // Select SMCLK, ACLK source

3.2.4 設定DCOCLK輸出的頻率範圍

- 使用UCSCTL1暫存器中的DCORSEL位來設定範圍

- 不用看UCSCTL0暫存器中的DCO和MOD位,微控制器會自動設定

- 儘可能讓輸出的頻率在DCORSEL控制的範圍的中間位置

3.2.5 UCS模組失效安全操作

- 任何一種失效都會導致OFIFG(振盪器失效中斷、非遮蔽)

- 受到OFIE使能位控制

- 振盪器關閉、開啟但未正常工作時,對應振盪器失效位XT1 LFOFFG,XT1 HFOFFG, XT2OFFG置位;

- 振盪器失效位一旦置位必須使用者軟體清除;

- 若使用者軟體清除振盪器失效位後失效條件依然存在,振盪器失效位會自動置位。

- 振盪器失效事件不受GIE控制。

3.3 低功耗

| 模式 | 作用 |

|---|---|

| Active | 都可用FLL開 |

| LPM0 | ACLK、SMCLK可用 FLL開 |

| LPM3 | 僅ACLK可用(我發現這個和LPM2差不多) |

| LPM4 | 都不可用(軟體關機) |

- 最常用的開啟低功耗的方式

__bis_SR_register(LPM3_bits);//開啟低功耗模式3

__bic_SR_register(LPM3_bits);//關閉低功耗模式3

//也可以這樣:

LPM3;//開啟

LPM3_EXIT;//關閉

第四章 數字I/O模組

4.1 數字I/O模組暫存器設定

| 暫存器 | 名稱 | 0 | 1 | 復位值 |

|---|---|---|---|---|

| PxIN | 輸入暫存器 | 輸入低 | 輸入高 | 不確定 |

| PxOUT | 輸出暫存器 | 輸出低 | 輸出高 | 不確定 |

| 決定上下拉輸入 | 下拉 | 上拉 | 不確定 | |

| PxDIR | 方向暫存器 | 輸入(預設) | 輸出 | 0 |

| PxREN | 上下拉暫存器 | 不使能 | 使能 | 0 |

| PxSEL | 引腳功能選擇 | I/O功能 | 片內外設 | 0 |

- 關於PxDIR,PxREN和PxOUT在正確I / O配置中的用法

| PxDIR | PxREN | PxOUT | I / O配置 |

|---|---|---|---|

| 0 | 0 | x | 輸入,無上下拉 |

| 0 | 1 | 0 | 下拉輸入 |

| 0 | 1 | 1 | 上拉輸入 |

| 1 | x | 0/1 | 輸出0/1 |

- 對於P1,P2引腳而言,具有中斷能力,利用PxIFG, PxIE,和PxIES 暫存器進行配置。

| 暫存器 | 名稱 | 0 | 1 | 復位 |

|---|---|---|---|---|

| PxIFG | 中斷標誌位 | 無中斷 | 有中斷在等待 | 0 |

| PxIE | 中斷使能位 | 不使能 | 使能 | 0 |

| PxIES | 中斷邊沿選擇 | 上升沿 | 下降沿 | 不確定 |

4.2 按鍵

4.2.1 關於上下拉

- 對於按鍵必須要有上下拉,因為要有預設的輸入值,不能讓輸入值處於浮空狀態

- 可以選擇內部的上下拉和外部的上下拉

- MSP430F6638具有內部上下拉,所以不一定必須使用外部上下拉

4.2.2 按鍵消抖

- 軟體消抖:在首次檢測到按鍵按下後,先執行一段延時子程式,然後再次確認按鍵是否按下,達到消抖目的。

- 硬體消抖:常用雙穩態電路、單穩態電路和RC積分電路等方法。

4.3 額外的東西

對於在中斷服務函式中手動清零中斷標誌位IFG,其實有一種更方便的方法老師沒講——PxIV,這個東西會在後邊講Timer_A中看到類似的暫存器——TAxIV

- 讀/寫這個暫存器都會使得正在等待處理的最高中斷標誌位清零

- 如果有多箇中斷同時到來,那麼處理完最高中斷後會從新開啟一箇中斷。

第5章 看門狗WDT_A

5.1 看門狗概述

5.1.1 看門狗的作用

看門狗(Watchdog Timer-WDT)分硬體看門狗和軟體看門狗,用於程式跑飛時的系統復位。

5.1.2 程式跑飛

程式跑飛不是一種硬體故障,但它會引起宕機。

5.1.3 看門狗是什麼

簡單的說是一個定時器,從程式開始執行的時候就開始計數,當計數滿的時候就會使程式復位。所以要在計滿之前讓看門狗定時器的數值清零,俗稱喂狗。如果在計滿之前看門狗沒有收到喂狗訊號,則認為程式已經跑飛。

5.1.4 看門狗的兩種功能

- 分別是看門狗模式和間隔定時器模式

- 這兩種模式使用不同的中斷向量,但是都是單源中斷(所以中斷標誌位

WDTIFG可以自動清零)- 看門狗模式的中斷是系統中斷

- 間隔定時器的中斷是可遮蔽中斷

- 看門狗和間隔定時器使用相同的中斷標誌位:WDTIFG

- 這兩種模式不能同時使用

- 看門狗模式具有時鐘故障保護功能,但是間隔定時器模式沒有

5.2 看門狗的預設復位時間

WDTIS預設為4h,其時鐘訊號預設為SMCLK,而SMCLK的時鐘源預設為DCOCLKDIV,DCOCLKDIV的頻率預設為1048576Hz,所以時間間隔預設為

5.3 時鐘故障保護

- 為保證WDT在看門狗模式下能工作,如果SMCLK或ACLK作為WDT_A時鐘源發生故障,WDT將自己的時鐘自動調整為VLOCLK(注意這裡是VLOCLK,而不是

REFOCLK) - WDT_A提供故障安全時鐘功能,確保在看門狗模式下不能禁止WDT_A的時鐘。 這意味著LPM可能會受到WDT_A時鐘選擇的影響。

- 當WDT_A模組用於間隔定時器模式時,WDT A中沒有用於時鐘源的故障安全功能。

5.4 低功耗模式下的操作

用程式的要求和使用的時鐘型別決定了WDT_A的配置方式。 例如,如果使用者想要使用LPM3,則WDT_A不應配置為看門狗模式,其時鐘源最初來自DCO,XT1為高頻模式,XT2為SMCLK或ACLK。 在這種情況下,SMCLK或ACLK將保持啟用狀態,從而增加LPM3的當前消耗。

5.5 關閉看門狗的方法

//1. 正確的方法

WDTCTL = (WDTPW + WDTHOLD);

WDTCTL = WDTPW | WDTHOLD;

//2. 錯誤的方法

WDTCTL |= (WDTPW + WDTHOLD);//錯誤

第6章 定時器Timer_A

6.1 各種暫存器(x代表數字,比如我們用的TA1,那麼x=1)

6.1.1 TAxR——16位計數器

- 16位定時器/計數器暫存器TAxR隨時鐘訊號的每個上升沿遞增或遞減(取決於工作模式)。 可以使用軟體讀取或寫入TAxR。 另外,定時器在溢位時可以產生中斷。

- 可以通過將TAxCTL暫存器中的TACLR位置1來清零TAxR。 將該位置1會復位TAxR,定時器時鐘分頻器邏輯和計數方向。 TACLR位自動復位,始終讀為0。

6.1.2 TAxCTL——時鐘控制

- TASSEL——選擇時鐘

- MC——設定計數模式

| MC | Mode | 中文 | Description |

|---|---|---|---|

| 00 | Stop | 停止計數 | 定時器停止 |

| 01 | Up | 增計數 | 定時器重複從零計數到TAxCCR0的值 |

| 10 | Continuous | 連續計數 | 定時器重複從零到0FFFFh。 |

| 11 | Up/down | 增減計數 | 定時器重複從零開始計數到TAxCCR0的值並返回到零。 |

- TACLR——清空TAxR

- TAIE——中斷使能

6.1.3 TAxCCTLn——Timer_Ax捕捉/比較控制暫存器n

捕獲比較模組一共7個,n=(0~6)

- CAP——設定捕獲模式/比較模式

- OUTMOD——設定輸出方式(共8種)

- 第一種是電平輸出,可以指定輸入的電平(OUT位)

- 模式 2, 3, 6, and 7 對於 TAxCCR0 是沒有用的因為 EQUx = EQU0.

- CCIE——中斷使能

【注意】:這個是捕獲比較的中斷使能,和上面的Timer_A的中斷不同。

6.1.4 TAxCCRn——捕捉/比較暫存器n

放數的

6.1.5 TAxIV——中斷暫存器

- 用於查詢是哪個中斷到來

- 其中包含的中斷事件不包括TAxCCR0中斷

6.2 中斷

6.2.1TAxCCR0中斷

- TAxCCR0 CCIFG具有最高的Timer_A中斷優先順序,並具有專用中斷向量(TIMER0_A0_VECTOR)。 當TAxCCR0中斷請求被服務時,TAxCCR0 CCIFG自動復位。

- 這是一個單源中斷

6.2.2 TAxIV中斷

- TAxCCRy CCIFG和TAIFG被優先化並組合以獲得單箇中斷向量。

(這表明其優先順序可以被軟體設定,這和所謂中斷優先順序是兩個概念)這話大錯特錯!!優先順序不能設定,寫錯了! - TAxIV用於確定請求中斷的標誌。

- 禁用Timer_A中斷不會影響TAxIV值。

- TAxIV暫存器的任何訪問,讀取或寫入都會自動重置最高的待處理中斷標誌。 如果設定了另一箇中斷標誌,則在服務初始中斷後立即產生另一箇中斷。(如果你們做過實驗會發現後邊的串列埠通訊也有這個性質)

- 這是一個多源中斷,但是不用手動清中斷標誌位

6.3 程式

6.3.1 TA0CCR0 中斷

下面程式採用增計數模式,那麼增加到TA0CCR0 就會產生TA0CCR0 中斷,然後計數器自動清零,重新計數

- 【注意】:這是一個單源中斷

#include<msp430f6638.h>

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P4DIR |= BIT1; // P4.1 output

TA0CCTL0 = CCIE; // 開啟TA0CCR0 的中斷

TA0CCR0 = 50000;

TA0CTL = TASSEL__SMCLK + MC__UP + TACLR; // 時鐘源選SMCLK,增計數模式,清零計數器

_BIS_SR(LPM0_bits + GIE); // Enter LPM0, enable interrupts

_NOP(); // For debugger

}

// Timer_A0 ISR

#pragma vector=TIMER0_A0_VECTOR

__interrupt void TIMER0_A0_ISR(void) // 注意這個中斷向量

{

P4OUT

}

6.3.2 TAxIV中斷

下面程式,由於是連續計數模式,計數器會從0到FFFF重複計數,但是又未設定TA0CCRn的值,所以只在0FFFFh的時候才產生TAIFG這個中斷,這個中斷的查詢在TAxIV=14的位置

- 【注意】:這是多源中斷

#include<msp430f6638.h>

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; // Stop WDT

P4DIR |= BIT1; // P4.1 output

TA0CTL = TASSEL__ACLK + MC__CONTINUOUS + TACLR + TAIE; // 時鐘源為ACLK,連續計數模式,清空計數器,是能中斷

__bis_SR_register(LPM3_bits + GIE);

//【區分】:__bic_SR_register()這個函式是和上面的作用相反,

//比如__bic_SR_register(LPM0_bits + GIE);是關閉低功耗並且關閉總中斷

_NOP();

}

#pragma vector=TIMER0_A1_VECTOR // 這個中斷向量和上面的程式不一樣

__interrupt void TIMER0_A1_ISR(void)

{

switch(__even_in_range(TA0IV,14))// __even_in_range()本徵函式,用於多源中斷的查詢。

{

case 0: break; // No interrupt

case 2: break; // CCR1 not used

case 4: break; // CCR2 not used

case 6: break; // reserved

case 8: break; // reserved

case 10: break; // reserved

case 12: break; // reserved

case 14: P4OUT ^= BIT1; // TAIFG

break;

default: break;

}

}

第7章 模數轉換器ADC12_A

7.1 概述

7.1.1 ADC12

- 這是一個12位的模擬量轉換為數字量的內部外設

- 主要的過程為:

- 將模擬量通過某個微控制器的引腳輸入進去

- ADC讀取該引腳的電壓值,並根據參考電壓的大小,將其轉化為12位的數字量的值

- 將這個12位的數字值儲存到一個12位暫存器中

- 在ADC12的中斷服務函式中讀取這個暫存器的值,從而進行相應的操作

7.1.2 解析度

- 用數字量的二進位制位數來表示。如12位ADC的解析度就是12位

- 用1個LSB使輸出變化的程度表示,如12位ADC的解析度為滿刻度的1/212

7.1.3 量化間隔

- 滿量程輸入電壓/(2n-1)

- 其中n為ADC的位數,這裡為12

- 滿量程輸入電壓一般為正參考電壓,即VR+

7.1.4 量化誤差

是ADC的有限位數對模擬量進行量化而引起的誤差,有兩種計算方法:

- 絕對誤差=量化間隔/2

- 相對誤差=1/(2n+1)

- 這裡的n還是12

7.1.5 關於參考電壓的選取(REFMSTR的設定)

在REFCTL這個暫存器中有一個神奇的位叫做REFMSTR,可以通過它來設定由誰控制ADC12的參考電壓。

- 當REFMSTR=1時,ADC12允許通過REFCTL暫存器控制參考系統,ADC暫存器組(ADC12REFON,ADC12REF2_5,ADC12TCOFF和ADC12REFOUT)內的原先的控制位就失去了作用,但是 ADC12SR和ADC12REFBURST仍由ADC12_A控制,因為它們非常特定於ADC12_A模組。

- 當REFMSTR=0時,ADC12的參考電壓由它自己的暫存器組設定,就是上邊提到的那些暫存器

7.1.6 轉換的計算公式

- 其中4095的由來是

- 當輸入電壓大於正參考電壓時,暫存器的值為0x0fff,當輸入電壓小於負參考電壓時,暫存器的值為0x0000

7.2 ADC12的取樣

7.2.1 SHI

- 一次AD轉換由取樣輸入訊號SHI的上升沿觸發

- SHI的來源:

7.2.2 SAMPCON

- 取樣控制訊號SAMPCON控制取樣週期和轉換開始,當SAMPCON 為高時取樣啟用, SAMPCON 的下降沿觸發模數轉換。

- ADC12SHP 定義了2種取樣時序(方法):

- 擴展采樣模式

SAMPCON的長度由SHI的時間控制。即,取樣輸入訊號SHI直接作為取樣控制訊號SAMPCON,決定取樣的起始時刻、取樣週期和轉換時刻 - 脈衝取樣模式

脈衝取樣模式下,取樣輸入訊號SHI僅用於觸發取樣,取樣週期由取樣定時器(ADC12SHT0x和ADC12SHT1x設定)確定

- 擴展采樣模式

7.3 各種暫存器

7.3.1 ADC12CTL0

- ADC12SHT1x & ADC12SHT0x

- 用於設定取樣的週期,其中

- ADC12SHT1x配置ADC12MEM8 ~ADC12MEM15暫存器的取樣週期

- ADC12SHT0x配置ADC12MEM0 ~ADC12MEM7暫存器的取樣週期

- ADC12REF2_5V

內部參考電壓的設定 - ADC12REFON

內部參考電壓開啟/關閉 - ADC12ON

ADC12的開啟/關閉 - ADC12ENC

ADC12_A的轉換使能,這個位在配置暫存器之前應該置0,配置結束後置1 - ADC12SC

ADC12的轉換開始,這個位在轉換結束後會自動復位,所以在應用程式中轉換結束後應該將這一位軟體置1

7.3.2 ADC12CTL1

- ADC12CSTARTADDx

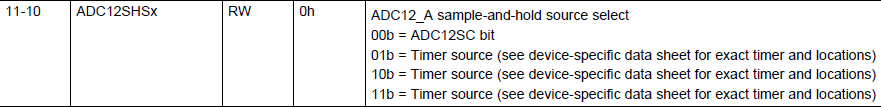

轉換地址選擇,即ADC12MEMx的選擇 - ADC12SHSx

SHI訊號選擇 - ADC12SHP

取樣模式選擇(擴展采樣和脈衝取樣) - ADC12SSELx

ADC12CLK的選擇 - ADC12CONSEQx

模式選擇,一般選擇單通道單次轉換,即00

7.3.3 ADC12MEMx

轉換出來的值存放在這裡,一般在終端服務函式中檢視這個暫存器。當轉換結果寫入選定的ADC12MEMx, ADC12IFGx中對應標誌位置位;當這個暫存器的值被讀取之後,IFG自動復位。

- 強調一下:轉換結果寫入ADC12MEMx時對應的ADC12IFGx置位,若對應的ADC12IEx 和GIE 置位,將會產生中斷請求。

7.3.4 ADC12MCTLx

這裡的x是由ADC12CTL1暫存器中的ADC12CSTARTADDx位確定的

- ADC12SREFx參考電壓選擇

- ADC12INCHx模擬量輸入通道選擇

7.3.5 ADC12IE

中斷使能暫存器,使能哪一位也是由ADC12CTL1暫存器中的ADC12CSTARTADDx位確定的

7.3.6 ADC12IV

這個暫存器可以檢視是哪個中斷標誌位置位,具體的程式碼是:

switch(__even_in_range(ADC12IV,34))// 注意這個內建函式,用於檢視是哪個中斷到來

{

case 0: break; // Vector 0: No interrupt

case 2: break; // Vector 2: ADC overflow

case 4: break; // Vector 4: ADC timing overflow

case 6: break;// Vector 6: ADC12IFG0

case 8: break; // Vector 8: ADC12IFG1

case 10: break; // Vector 10: ADC12IFG2

case 12: break; // Vector 12: ADC12IFG3

case 14: break; // Vector 14: ADC12IFG4

case 16: break; // Vector 16: ADC12IFG5

case 18: break; // Vector 18: ADC12IFG6

case 20: break; // Vector 20: ADC12IFG7