【 Vivado 】輸入延遲約束(Constraining Input Delay)

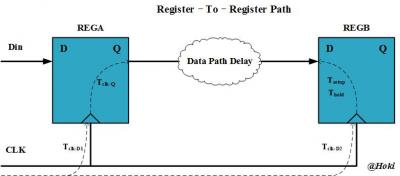

前幾篇博文提到了四種時序路徑:基本的時序約束、分析的概念

1) FPGA內部時序單元間的路徑

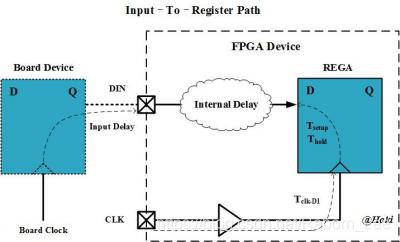

2) 輸入埠到FPGA內部時序單元的路徑

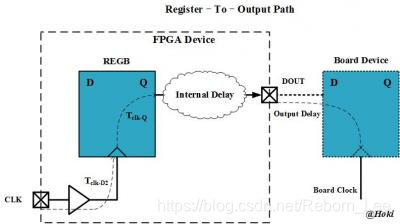

3) FPGA內部時序單元到輸出埠的路徑

4) 輸入埠到輸出埠的路徑

其中1. FPGA內部時序單元間的路徑中,時序分析所需要的時間引數:Tclk-D1, Tclk-Q, Tdata_path_delay, Tclk_D2, Tsetup, Thold

其它兩條路徑都相應缺少FPGA外部的幾個時間引數,這些引數都需要通過時序約束告知Vivado,然後Vivado才能精確地進行這些路徑的時序分析。這一節先介紹

2. 輸入埠到FPGA內部時序單元的路徑這條路徑的約束。

在輸入埠到FPGA內部時序單元的路徑中,Input Delay這段路徑是在FPGA外部,因此需要約束設定其時間引數,通過set_input_delay約束命令約束,具體如下:

set_input_delay

另外根據source clock和destination clock,輸入介面可分為以下兩種情況:

System Synchronous Input

分析輸入埠到FPGA內部時序單元的路徑時,當source clock和destination clock來自同一個系統時鐘時,稱為系統同步輸入(system synchronous input)。

create_clock -name CLKB -period 10 -waveform {0 5} [get_ports {CLKB}]

(圖1)

其中Tclkd_ext表示外部時鐘源到外部晶片的延時;Tclkd_int表示外部時鐘源到FPGA輸入埠的延時;Tco表示外部晶片tCO時間;Tbd表示外部晶片輸出埠到FPGA晶片的板上延時。

對應max_input_delay和min_input_delay,以上幾個時間引數都有max和min值,約束如下:

set_input_delay -clockCLKB-max [Tclkd_ext_max + Tco_max + Tbd_max – Tclkd_int_min] [get_portsDIN]

set_input_delay -clockCLKB-min [Tclkd_ext_min + Tco_min + Tbd_min – Tclkd_int_max] [get_portsDIN]

Source Synchronous Input

分析輸入埠到FPGA內部時序單元的路徑時,當destination clock來自外部晶片,即與資料輸入同源,稱為源同步輸入(source synchronous input)。

結構如圖2所示,從板上晶片輸入到FPGA除了有資料,還有一個隨路時鐘,是由板上晶片產生的。

(圖2)

Input Delay Value:

約束Input Delay分max值和min值,參考圖2中時間引數,其中Tcd表示外部晶片時鐘輸出到FPGA輸入埠的延時;Tco表示外部晶片tCO時間;Tbd表示外部晶片輸出埠到FPGA晶片的板上延時。Input delay的計算式如下:

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

Clock & Data:

源同步輸入的約束相比於系統同步輸入的複雜些,其根據時鐘與資料的關係,可分為邊緣對齊(Edge Aligned Clock&Data)和中心對齊(Center Aligned Clock&Data)兩種:

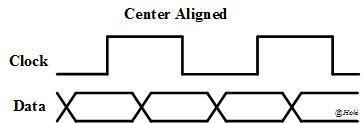

1) Center Aligned

中心對齊是指時鐘和資料到達後級時序單元時,時鐘沿在資料中心,如圖3所示。

在這種情況下可以直接使用時鐘採集資料。

(圖3)

約束如下:

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) Edge Aligned

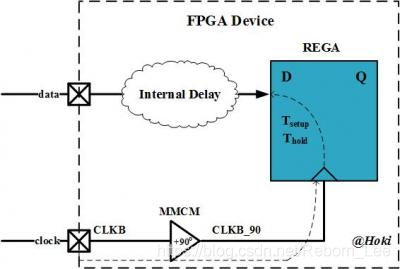

邊緣對齊是指時鐘和資料到達後級時序單元時,時鐘沿與資料變化沿重合,如圖4所示。

(圖4)

這種情況下顯然不滿足後級時序單元的Setup要求,因此時鐘需要經過一定的移相才能去採集資料,通常採用MMCM模組實現移相,如圖5所示。

圖(5)

時鐘約束如下:

create_clock -name CLKB -period clk_period [get_ports {CLKB}]

create_generated_clock -name CLKB_90 -source [get_clocks CLKB] –phase 90 [get_pins{MMCM|co[0]}]

set_input_delay -clock[get_clocks CLKB_90] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB_90] -min min_input_delay [get_ports indata] -add_delay

SDR & DDR:

源同步介面常用於高速資料傳輸,如DDR儲存器、HyperTransport匯流排和SPI-4.2標準介面等。其中DDR指雙倍速率資料採集(Double Data Rate),在時鐘的上升沿和下降沿都傳輸資料實現雙倍速率。

1) SDR(Single Data Rate)

單倍速率資料採集只在時鐘的上升沿或者下降沿採集資料,如圖6所示。

圖6

Input約束只需針對時鐘的上升沿或者下降沿進行,如:

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

2) DDR(Double Data Rate)

雙倍速率資料採集在時鐘的上升沿和下降沿都採集資料,如圖7所示。

(圖7)

針對時鐘的上升沿和下降沿都需要進行Input約束,如:

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata]

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -add_delay

set_input_delay -clock[get_clocks CLKB] -max max_input_delay [get_ports indata] -clock_fall -add_delay

set_input_delay -clock[get_clocks CLKB] -min min_input_delay [get_ports indata] -clock_fall -add_delay

Timing Check in Vivado

以上講解了如何進行Input delay的約束,可能大家還不明白為什麼需要約束input delay?那下面就講解一下input delay 在時序分析中的作用:

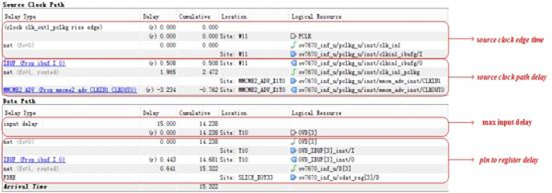

在Vivado中時序分析分為setup check和hold check,其中引入了setup slack和hold slack來界定時序是否收斂。在《2. Timing Basics》中介紹過FPGA內部register_to_register路徑setup slack和hold slack的計算方法,本文則介紹一下輸入埠到FPGA內部時序單元的路徑slack的計算方法,公式如下:

Setup check:

setup slack = data required time – data arrival time

其中:

data required time = destination clock edge time + destination clock path delay

- clock uncertainty

- setup time

data arrival time = source clock edge time + source clock path delay

+ max input delay

+ pin to register delay

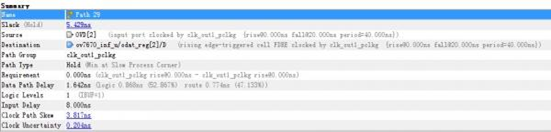

為了確認公式的正確性,開啟Vivado軟體,新建了一個約束了input delay的工程,如下幾圖所示為中其中一條路徑的setup check報告。

約束的時鐘週期為40ns,max input delay為15ns

data arrival time= 15.322ns

data required time = 40.199ns

時序報告中slack計算方式與公式完全一致,因此可以得到setup slack = data required time – data arrival time= 40.199ns – 15.322ns = 24.846ns。

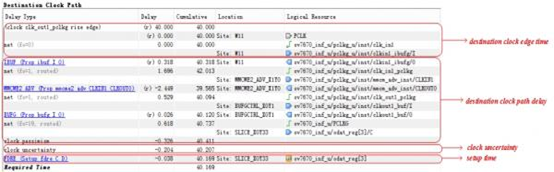

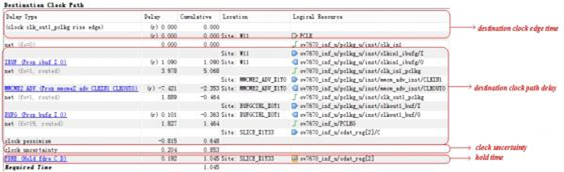

Hold check:

hold slack = data arrival time – data required time

其中

data required time = destination clock edge time + destination clock path delay

+ clock uncertainty

+ hold time

data arrival time = source edge time + source clock path delay

+ pin to register delay

+ min input delay

如下幾圖為Vivado軟體分析得到的hold check時序報告:

約束的min input delay = 8ns

data arrival time= 6.474ns

data required time= 1.045ns

時序報告中slack計算方式與公式完全一致,因此可以得到hold slack = data arrival time – data required time= 6.474ns – 1.045ns = 5.429ns。