【 Vivado 】輸出延遲約束(Constraining Ouput Delay)

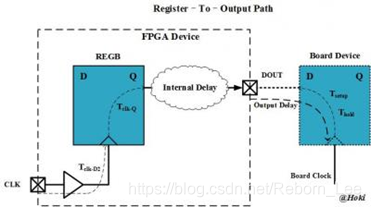

FPGA內部時序單元到輸出埠的路徑也需要約束其output delay,如圖1所示框圖。

圖1

約束output delay的命令是set_output_delay,具體的引數如下:

set_output_delay –clock reference_clock –min/-max delay_value

[get_ports {DOUT}] [-clock_fall] [-add_delay]

-min/-max表示設定output delay的最小和最大值;

-clock_fall表示output delay是針對關聯時鐘的下降沿;

-add_delay表示對同一個輸出埠約束不同的output delay值,一般是在如DDR需要約束兩個時鐘沿的output delay,或者輸出埠後級連線了多個器件對應不同的時鐘約束的情況下,需要加入此引數。

與輸入介面約束類似,輸出介面的約束也可分為以下兩種情況:

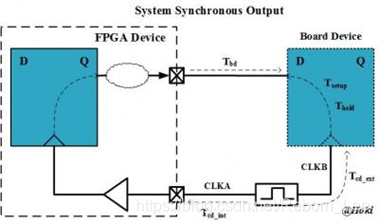

System Synchronous Output

分析FPGA內部時序單元到輸出埠的路徑時,當source clock和destination clock來自同一個系統時鐘時,稱為系統同步輸出(system synchronous output)。

此處需要引入虛擬時鐘(virtual clock)的概念,在講時鐘約束的一節時有提到,當source clock or destination clock不在FPGA設計中時,則需要約束一個虛擬時鐘。如圖2所示為系統同步輸出路徑框圖,source clock

create_clock -name CLKA-period 10 -waveform {0 5} [get_ports {CLKA}]

create_clock -name CLKB-period 10 -waveform {0 5}

圖2

其中Tcd_ext表示外部時鐘源到外部晶片的延時;Tcd_int表示外部時鐘源到FPGA時鐘埠的延時;Tsetup表示外部晶片tsu時間;Thold表示外部晶片thd時間;Tbd表示FPGA輸出埠到外部晶片的板上延時。

Output delay value的計算式如下:

max_output_delay = Tbd_max + Tsetup + Tcd_int_max - Tcd_ext_min

min_output_delay = Tbd_min – Thold + Tcd_int_min - Tcd_ext_max

相比於input delay value,上式相對於難理解些,那就推導一下,深入理解:

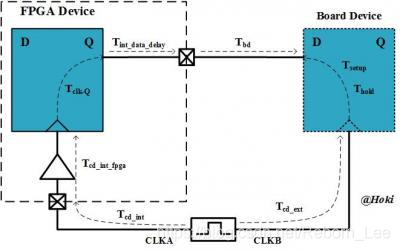

將此路徑假想為FPGA內部register_to_register路徑作分析,如圖3所示,

圖3

在博文:https://blog.csdn.net/Reborn_Lee/article/details/85295160,介紹了時序分析分為Setup Check和Hold Check:

- Setup Check

setup slack = (destination clock edge time - source edge time)

+ (destination clock path delay - source clock path delay)

- clock uncertainty

- setup time

- clock to output time

- data path delay

將圖3中路徑的時間引數代入可得:

setup slack = Tclk_period + (Tcd_ext – Tcd_int – Tcd_int_fpga) – Tclk_uncertainty – Tsetup – Tclk-Q– Tint_data_delay - Tbd

其中Tcd_ext,Tcd_int,Tsetup和Tbd都是FPGA外部的時間引數,需要通過約束告知vivado,上式整理一下可得:

setup slack = Tclk_period – Tcd_int_fpga – Tclk_uncertainty – Tclk-Q – Tint_data_delay

+ (Tcd_ext – Tcd_int) – Tsetup - Tbd = Tclk_period – Tcd_int_fpga – Tclk_uncertainty

– Tclk-Q – Tint_data_delay –Tmax_output_delay

Tmax_output_delay = Tsetup + Tbd_max + Tcd_int_max - Tcd_ext_min,與前文中max_output_delay的計算式相同。

- Hold Check

hold slack = (source clock edge time - destination edge time)

+(source clock path delay - destination clock path delay)

- clock uncertainty

- hold time

+ clock to output time

+ data path delay

= (Tcd_int + Tcd_int_fpga - Tcd_ext)

- Tclk_uncertainty

– Thold

+ Tclk-Q

+ Tint_data_delay + Tbd

其中Tcd_ext,Tcd_int,Thold和Tbd都是FPGA外部的時間引數,需要通過約束告知vivado,上式整理一下可得:

hold slack = Tcd_int_fpga - Tclk_uncertainty + Tclk-Q + Tint_data_delay + Tbd – Thold + Tcd_int - Tcd_ext

= Tcd_int_fpga - Tclk_uncertainty + Tclk-Q + Tint_data_delay + Tmin_output_delay

Tmin_output_delay = Tbd_min – Thold + Tcd_int_min - Tcd_ext_max,與前文中min_output_delay的計算式相同。

可以發現在setup check中使用max output delay,hold check使用min output delay,都是使slack的值較小的趨勢,這樣使FPGA內部的時序條件更嚴苛,如果在這種條件下時序收斂,就絕對能保證設計的穩定性。

經過上面的推導,迴歸系統同步輸出主題,約束命令如下:

set_output_delay -clockCLKB -max max_output_delay [get_ports {DOUT}]

set_output_delay -clockCLKB -min min_output_delay [get_ports {DOUT}

-

- Source Synchronous Output

分析FPGA內部時序單元到輸出埠的路徑時,輸出到外部晶片的時鐘與資料是同源的,稱為源同步輸出(source synchronous output)。

結構如圖4所示,從FPGA輸出到外部晶片除了有資料,還有一個隨路時鐘,由FPGA內部時鐘模組產生的。

圖4

參考圖4中時間引數,其中Tcd表示時鐘從FPGA輸出到外部晶片輸入埠的延時;Tsetup表示外部晶片tSU時間;Thold表示外部晶片tH時間;Tbd表示FPGA輸出埠到外部晶片的板上延時。Output delay的計算式如下(推導與系統同步輸出類似,不再累述):

max_output_delay = Tbd_max + Tsetup - Tcd_min

min_output_delay = Tbd_min – Thold - Tcd_max

源同步輸出的output delay約束命令如下:

set_output_delay -clockCLKB -max max_output_delay [get_ports {DOUT}]

set_output_delay -clockCLKB -min min_output_delay [get_ports {DOUT}]