【 Vivado 】輸入延遲約束例項

上篇博文講了輸入延遲約束( Input Delay Constraints):輸入延遲約束(Constraining Input Delay)

這篇博文講解具體的例項,通過例項去學習是最有效果的。

例項1

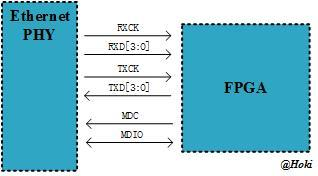

如圖1所示系統,乙太網PHY晶片與FPGA相連,分為三組介面:

RX介面:時鐘RXCK和資料RXD;

TX介面:時鐘TXCK和資料TXD;

MII管理介面:時鐘MDC和資料MDIO。

(圖1)

其中RX介面屬於源同步輸入介面,以下就以RX介面為例講解一下約束input delay:

Clock Constraints

首先約束時鐘,如圖2所示為PHY(DP83849ID)在100Mb/s模式下的時序圖,時鐘和資料為Center Aligned關係,因此時鐘在FPGA中無需再移相,可直接使用RXCK採集資料,時鐘約束如下:

create_clock –name RXCK –period 40 –waveform {0 20} [get_ports {RXCK}]

(圖2)

Input Delay Value

根據上節中源同步輸入計算Input Delay的公式:

max_input_delay = Tbd_max + Tco_max - Tcd_min

min_input_delay = Tbd_min + Tco_min - Tcd_max

Tbd為資料線RXD在板上的延時,也就是訊號在電路板上的傳播時間。查找了網上的一些資料:

“訊號速度還與不同材料的介電常數相關,具體計算公式是 V=C/Er0.5

在此例中,通過PCB設計軟體計算得到RXD[3:0]的走線長度,分別是LRXD[3]=426mil,LRXD[2]=451mil,LRXD[1]=502mil,LRXD[0]=406mil,因此可以計算得到:

Tbd_max = 502mil * 166ps/inch = 0.083332ns

Tbd_min = 406mil * 166ps/inch = 0.067396ns

Tcd為時鐘線RXCK在板上的延時,走線長度LRXCK=399mil,因此可以計算得到:

Tcd_max=Tcd_min=399mil * 166ps/inch = 0.066234ns

Tco為RX介面clock_to_output時間,如圖2中,等於T2.5.2時間引數,因此可得到:

Tco_max = 30ns

Tco_min = 10ns

綜上:

max_input_delay = Tbd_max + Tco_max - Tcd_min = 0.083332ns + 30ns - 0.066234ns = 30.017098ns

min_input_delay = Tbd_min + Tco_min - Tcd_max = 0.067396ns + 10ns - 0.066234ns = 10.001162ns

Constraints

很顯然,RX介面為SDR,時鐘約束和input delay值的計算後,可以對input delay進行約束,命令如下:

set_input_delay -clock[get_clocks RXCK] -max 30.017098[get_ports {RXD[3] RXD[2] RXD[1] RXD[0]}]

set_input_delay -clock[get_clocks RXCK] -min 10.001162[get_ports {RXD[3] RXD[2] RXD[1] RXD[0]}]

在Vivado的GUI介面中也可以進行約束,設計經過綜合實現後,開啟編輯約束檔案,如圖3所示

(圖3)

選擇Set Input Delay,在右側雙擊,可彈出Input Delay設定視窗,如圖4所示

(圖4)

在彈出的Input Delay視窗中設定引數,如圖5所示,Input Delay約束完成。

(圖5)

例項2

在例項1中,如圖1所示,對RX介面進行了約束。另外MII管理介面,其中MDIO是雙向資料介面,肯定需要input delay的約束

(圖1)

最初以為MII介面屬於源同步輸入,但是仔細檢視後發現不對勁兒,時鐘MDC並不是由PHY提供的,而是FPGA輸出給PHY的,這與源同步介面的定義矛盾,源同步需要時鐘和資料來自同一個源。因此只能劃分到系統同步輸入範疇了,仔細一想還是能說得通的,系統同步中只要求source clock和destination clock來自同一個時鐘網路即可,不管是在FPGA外部還是內部,如圖2所示,

(圖2)

系統同步輸入的input delay value計算公式如下:

max input delay = Tclkd_ext_max + Tco_max + Tbd_max – Tclkd_int_min

min input delay = Tclkd_ext_min + Tco_min + Tbd_min – Tclkd_int_max

此例的情況,時鐘源到FPGA輸入埠的延時Tclkd_int等於0,時鐘源到外部晶片的延時為TCD,因此得到變化後的公式如下:

max input delay = TCD_max + TCO_max + TBD_max

min input delay = TCD_min + TCO_min + TBD_min

各時間引數的計算如下:

TCD :時鐘線MDC在板上的長度LMDC=489mil,TCD_max= TCD_min=489mil*166ps/inch= 0.081174ns

TBD:資料線MDIO在板上的長度LMDIO=634mil,TBD_max= TBD_min=634mil*166ps/inch= 0.105244ns

TCO: 參考PHY(DP83849ID)的手冊,如圖3所示,TCO等於時間引數T2.3.1,得到TCO_max=30ns,TCO_min=0ns。

圖3

得到input delay值如下:

Max_input_delay = TCD_max + TCO_max + TBD_max

=0.081174ns+30ns+0.105244ns=30.186418ns

min input delay = TCD_min + TCO_min + TBD_min

=0.081174ns+0ns+0.105244ns=0.186418ns

綜上,MII管理介面的約束如下:

create_clock –name MDC –period 400 –waveform {0 200} [get_ports {MDC}]

set_input_delay -clock[get_clocks MDC] -max 30.186418[get_ports {MDIO}]

set_input_delay -clock[get_clocks MDC] -min 0.186418[get_ports {MDIO}]

在Vivado中的約束如圖4,5所示:

圖4、5、6