TMS320C6678外部儲存器DDR3硬體設計以及軟體除錯

阿新 • • 發佈:2019-01-23

文章主要介紹了一下,TMS320C6678 DSP的DDR3的硬體設計需要注意的問題以及相應的軟體除錯的問題。

------作者:jiangwenj02【轉載請註明】

一、硬體設計

本設計參考TI公司的樣板設計,在樣板的基礎上,為了節約成本和空間,刪除了DDR3的ECC。只留下4片Samsung公司的K4B1G1646G,總記憶體為512MB。DDR3擁有800、1066、1333、1600等多個數據傳輸頻率,設計使用1333資料傳輸頻率的DDR3,在除錯的時候可以使用低頻率的傳輸頻率進行逐步除錯。

DDR3資料傳輸速率最高達到1333MHz,屬於高速傳輸線。所以佈線的需要進行阻抗匹配。單線阻抗50歐姆,差分線阻抗100歐姆。

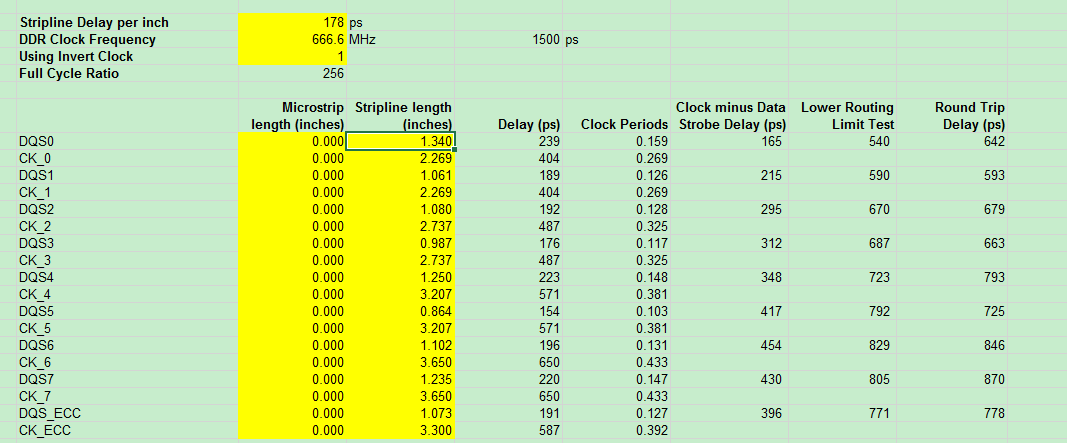

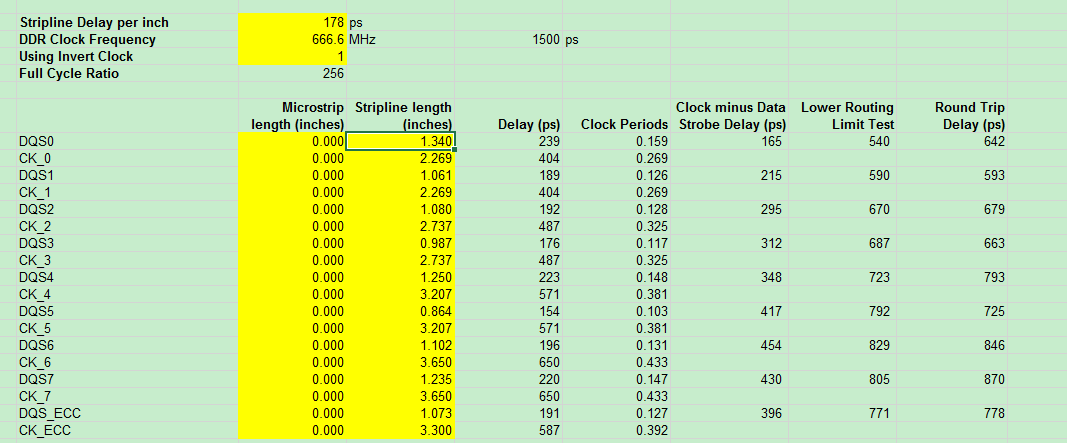

填寫內容有,DDR CLOCK FREQUENCY(時鐘頻率 1333/2,跑在其它速率只需要修改這個值)。修改DQS,CK中

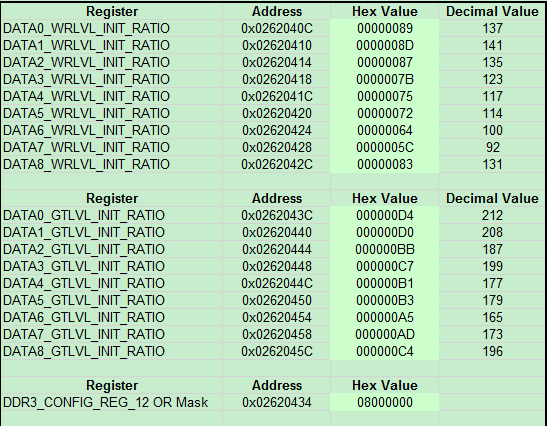

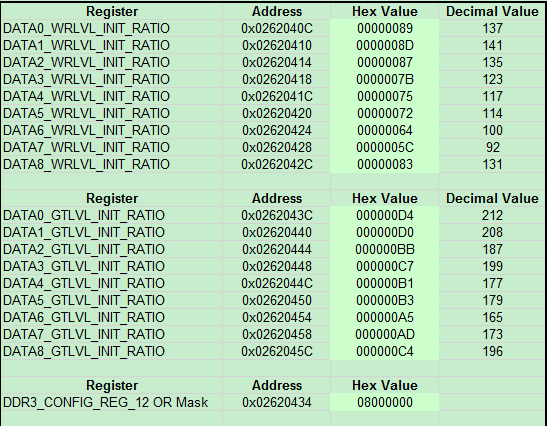

修改Memory_Test工程中,KeyStone_DDR_Init.c檔案中的C6678_EVM_DDR_Init函式中對應暫存器的值,如下。 //initial vale for leveling /*WRLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[2] = 0x89; gpBootCfgRegs->DDR3_CONFIG_REG[3] = 0x8D; gpBootCfgRegs->DDR3_CONFIG_REG[4] = 0x87; gpBootCfgRegs->DDR3_CONFIG_REG[5] = 0x7B; gpBootCfgRegs->DDR3_CONFIG_REG[6] = 0x75; gpBootCfgRegs->DDR3_CONFIG_REG[7] = 0x72; gpBootCfgRegs->DDR3_CONFIG_REG[8] = 0x64; gpBootCfgRegs->DDR3_CONFIG_REG[9] = 0x5C; gpBootCfgRegs->DDR3_CONFIG_REG[10] = 0x83; /*GTLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[14] = 0xD4; gpBootCfgRegs->DDR3_CONFIG_REG[15] = 0xD0; gpBootCfgRegs->DDR3_CONFIG_REG[16] = 0xBB; gpBootCfgRegs->DDR3_CONFIG_REG[17] = 0xC7; gpBootCfgRegs->DDR3_CONFIG_REG[18] = 0xB1; gpBootCfgRegs->DDR3_CONFIG_REG[19] = 0xB3; gpBootCfgRegs->DDR3_CONFIG_REG[20] = 0xA5; gpBootCfgRegs->DDR3_CONFIG_REG[21] = 0xAD; gpBootCfgRegs->DDR3_CONFIG_REG[22] = 0xC4; 修改完畢後,就可以執行DDR3測試程式。 注意:該工程會測試TMS320C6678,LL1、LL2、OTHER_L1、OTHER_L2、SL2。如果只是測試DDR3,可以修改mem_test_main.c檔案中的測試選項定義。 #define LL1_MEM_TEST 0 #define OTHER_L1_TEST 0 #define LL2_MEM_TEST 0 #define OTHER_L2_TEST 0 #define SL2_MEM_TEST 0 #define EXTERNAL_MEM_TEST 1 #define TEST_BY_DSP_CORE 1 #define TEST_BY_DMA 1 程式下載地址:http://download.csdn.net/detail/a137376864/9795887

填寫內容有,DDR CLOCK FREQUENCY(時鐘頻率 1333/2,跑在其它速率只需要修改這個值)。修改DQS,CK中

修改Memory_Test工程中,KeyStone_DDR_Init.c檔案中的C6678_EVM_DDR_Init函式中對應暫存器的值,如下。 //initial vale for leveling /*WRLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[2] = 0x89; gpBootCfgRegs->DDR3_CONFIG_REG[3] = 0x8D; gpBootCfgRegs->DDR3_CONFIG_REG[4] = 0x87; gpBootCfgRegs->DDR3_CONFIG_REG[5] = 0x7B; gpBootCfgRegs->DDR3_CONFIG_REG[6] = 0x75; gpBootCfgRegs->DDR3_CONFIG_REG[7] = 0x72; gpBootCfgRegs->DDR3_CONFIG_REG[8] = 0x64; gpBootCfgRegs->DDR3_CONFIG_REG[9] = 0x5C; gpBootCfgRegs->DDR3_CONFIG_REG[10] = 0x83; /*GTLVL_INIT_RATIO*/ gpBootCfgRegs->DDR3_CONFIG_REG[14] = 0xD4; gpBootCfgRegs->DDR3_CONFIG_REG[15] = 0xD0; gpBootCfgRegs->DDR3_CONFIG_REG[16] = 0xBB; gpBootCfgRegs->DDR3_CONFIG_REG[17] = 0xC7; gpBootCfgRegs->DDR3_CONFIG_REG[18] = 0xB1; gpBootCfgRegs->DDR3_CONFIG_REG[19] = 0xB3; gpBootCfgRegs->DDR3_CONFIG_REG[20] = 0xA5; gpBootCfgRegs->DDR3_CONFIG_REG[21] = 0xAD; gpBootCfgRegs->DDR3_CONFIG_REG[22] = 0xC4; 修改完畢後,就可以執行DDR3測試程式。 注意:該工程會測試TMS320C6678,LL1、LL2、OTHER_L1、OTHER_L2、SL2。如果只是測試DDR3,可以修改mem_test_main.c檔案中的測試選項定義。 #define LL1_MEM_TEST 0 #define OTHER_L1_TEST 0 #define LL2_MEM_TEST 0 #define OTHER_L2_TEST 0 #define SL2_MEM_TEST 0 #define EXTERNAL_MEM_TEST 1 #define TEST_BY_DSP_CORE 1 #define TEST_BY_DMA 1 程式下載地址:http://download.csdn.net/detail/a137376864/9795887