非阻塞賦值的內部延時和外部延時

學習verilog有一段時間了,從字面上理解,阻塞和非阻塞的區別很直白。 前者是序列,主要用於描述組合邏輯,和軟體中的賦值類似;後者是並行,主要用於描述時序邏輯。

但是和內部延時、外部延時混用在一起的時候,各種意想不到的情況就會發生。

下面將介紹,對於非阻塞賦值,內部延遲和外部延遲造成的結果就截然不同。

例1: 假設在5ns時刻pclock上出現一個正跳變沿;而current_state在正跳變出現之前的值為5,正跳變出現3ns後變為7, 下面兩個always語句中next_state_h和next_state_l的值將會是多少?

always @(posedge pclock) #7 next_state_h <= current_state; always @(posedge pclock) next_state_l <= #7 current_state;

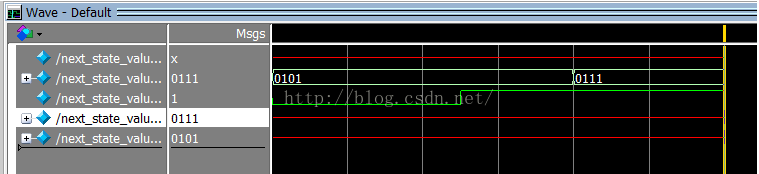

經分析,next_state_l <= #7 current_state 能分解為兩句話: 1) temp <= next_state_l; 2) #7 next_state_l <= temp; 所以儘管有7ns的delay,但next_state_l得到的還是pclock正跳變時所對應的current_state的值(5)。具體模擬結果如下

例2:根據已知的master_clock產生phase delay的slave_clock。

`timescale 1ns/1ps

module clock_shift(master_clk, slave_clk);

output reg master_clk;

output reg slave_clk;

parameter tON = 2, tOFF = 3, tDELAY = 5;

always

begin

#tON master_clk = 0;

#tOFF master_clk = 1;

end

always @(master_clk)

slave_clk <= #tDELAY master_clk;

endmodule

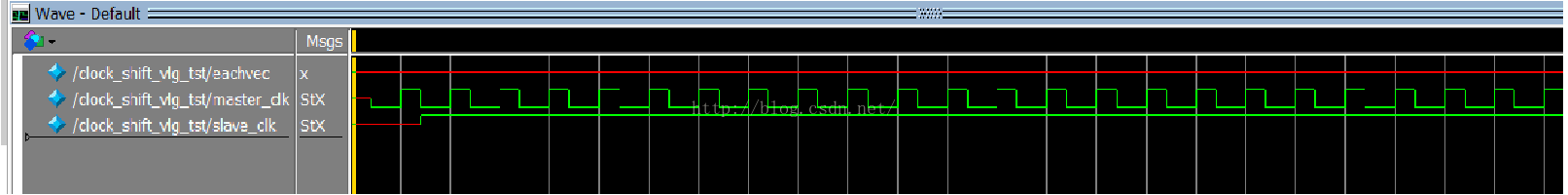

其模擬波形圖如下

但是如果將#tDELAY移到外部,如 #tDELAY slave_clk <= master_clk;則模擬圖形就會變成如下:

從這裡也可以看到,即使對於同一個非阻塞賦值, 內部delay和外部delay帶來的結果就完全不一樣。