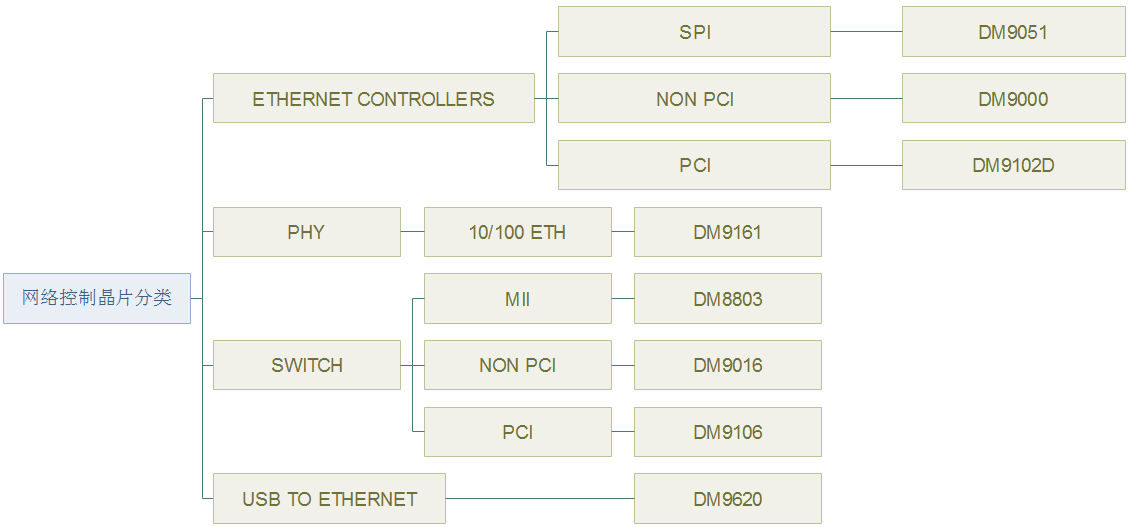

網路控制晶片分類

以DAVICOM公司網路控制晶片為例進行說明。

上面的晶片分類,是我學習了DAVICOM官網之後,自己畫的圖。可以瞭解一下。

我們做嵌入式開發的時候,會使用到網絡卡,那我們會根據主MCU和一些條件去選擇網絡卡晶片,上面的晶片都是網絡卡晶片,如何選擇啦?

1. ETHERNET CONTROLLERS

ETHERNETCONTROLLERS(乙太網控制器),此類別的網絡卡晶片是網絡卡控制器。

a. TheDM9051(I) is a fully integrated and cost-effective low pin count single chipFast Ethernet controller with a Serial Peripheral Interface (SPI), a 10/100MPHY and MAC, and 16K-byte SRAM.(DM9051(I)是一款完全整合且經濟高效的低引腳數單晶片快速乙太網控制器

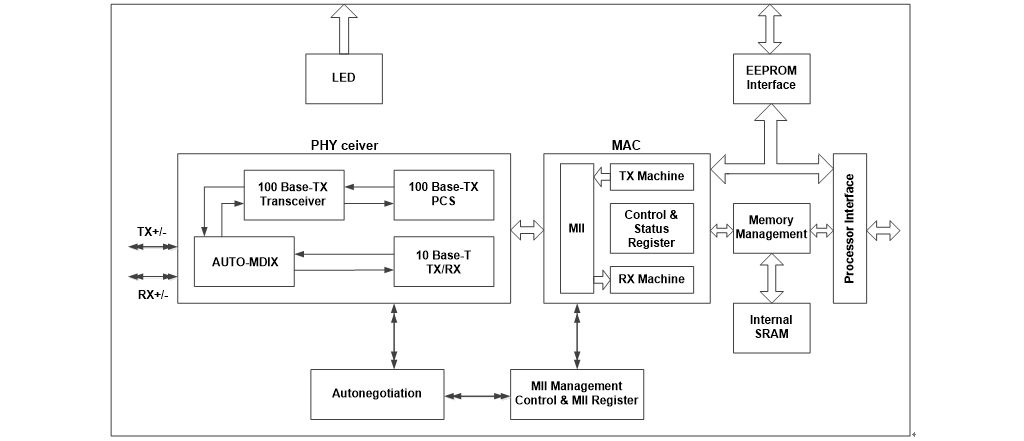

Block Diagram:

Processor Interface : SPI

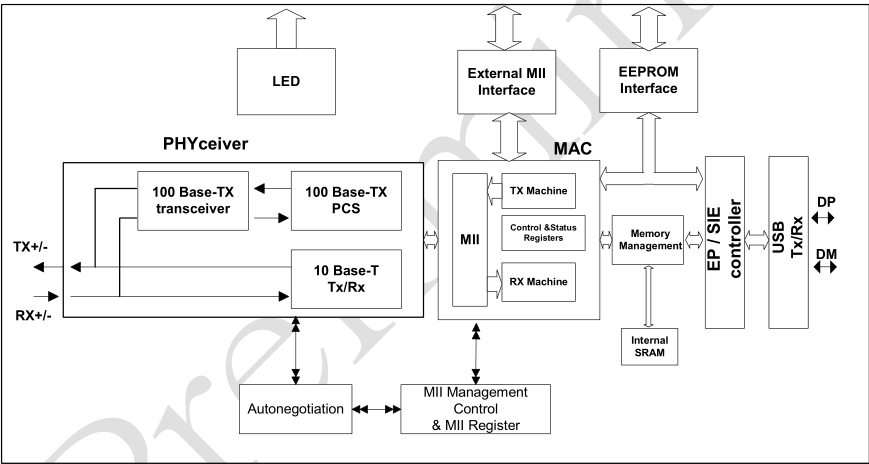

b. TheDM9000 is a fully integrated and cost-effective single chip Fast Ethernet MAC

controller with a general processor interface, a 10/100M PHY and4K Dword SRAM. (DM9000是一款完全整合且經濟高效的單晶片快速乙太網MAC

帶有通用處理器介面的控制器,10 / 100M PHY和4K Dword SRAM。)

Block Diagram:

The DM9000 also provides a MII interface to connect HPNA deviceor other transceivers that support MII interface. The DM9000 supports 8-bit,16-bit and 32-bit uP interfaces to internal memory accesses for differentprocessors.

processor interface: byte/word/dword of I/O command to internalmemory data operation

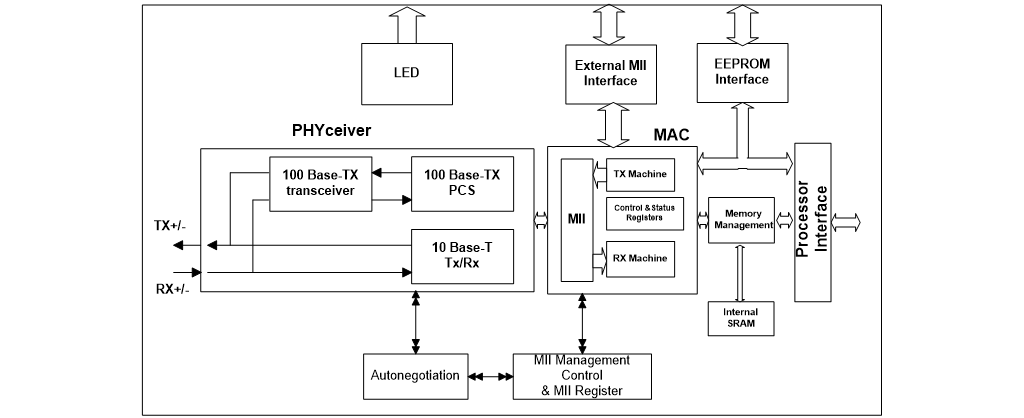

c. TheDM9102D is a fully integrated and cost effective single chip Fast Ethernet NIC controller.

The DM9102D provides direct interface to the PCI bus andsupports bus master mode to achieve the high performance of the PCI bus. Itfully complies with PCI 2.2.

Integrated Fast Ethernet MAC, Physical Layer and transceiver inone chip.

Block Diagram:

Interface : PCI.

小結:看Block Diagram和說明可知:DM9051,DM9000, DM9102D三款晶片的共同點是MAC + PHY。即這款晶片有PHY收發器也有MAC傳輸層控制器。不同點是,和MCU傳輸資料的時候,介面有差異,分別為SPI, NON PCI, PCI。

2. PHY

a. TheDM9161EP is a physical layer, single-chip, and low power transceiver for100BASE-TX 100BASE-FX and 10BASE-T operations.( DM9161EP是用於100BASE-TX 100BASE-FX和10BASE-T操作的物理層,單晶片和低功耗收發器。)

Through the Media Independent Interface (MII), the DM9161EPconnects to the Medium Access Control (MAC) layer, ensuring a highinter-operability from different vendors.( 通過媒體獨立介面(MII),DM9161EP連線到媒體訪問控制(MAC)層,確保不同的互操作性供應商。)

The DM9161EP uses a low power and high performance CMOS process.It contains the entire physical layer functions of 100BASE-TX as defined byIEEE802.3u, including the Physical Coding Sublayer (PCS), Physical MediumAttachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD),10BASE-TX Encoder/Decoder (ENC/DEC), and Twisted Pair Media Access Unit(TPMAU). The DM9161EP provides a strong support for the auto-negotiationfunction, utilizing automatic media speed and protocol selection. Furthermore,due to the built-in wave-shaping filter, the DM9161EP needs no external filterto transport signals to the media in 100MBASE-TX or 10MBASE-T Ethernetoperation.( DM9161EP採用低功耗和高效能CMOS工藝。 它包含IEEE802.3u定義的100BASE-TX的全部物理層功能,包括物理編碼子層(PCS),物理媒體附件(PMA),雙絞線物理介質相關子層(TP-PMD),10BASE-TX編碼器/解碼器(ENC/ DEC)和雙絞線媒體訪問單元(TPMAU)。該DM9161EP為自動協商功能提供強有力的支援自動媒體速度和協議選擇。此外,由於內建波形整形濾波器,DM9161EP不需要外部濾波器來傳輸訊號媒體採用100MBASE-TX或10MBASE-T乙太網操作)

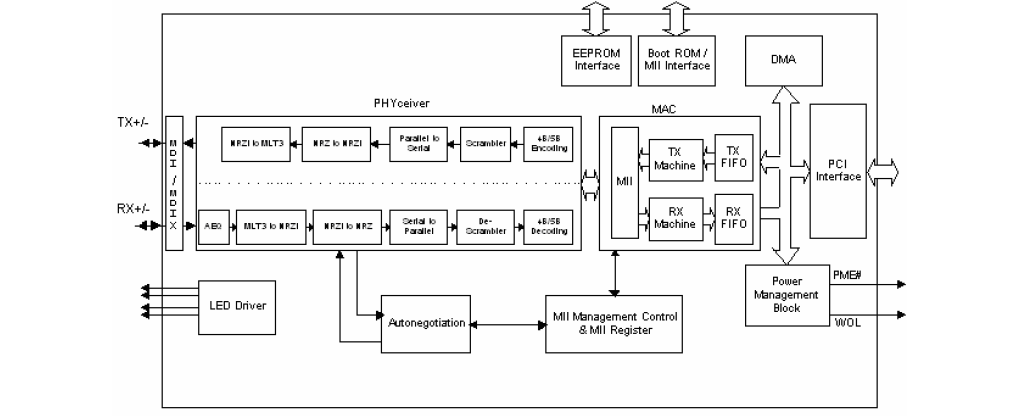

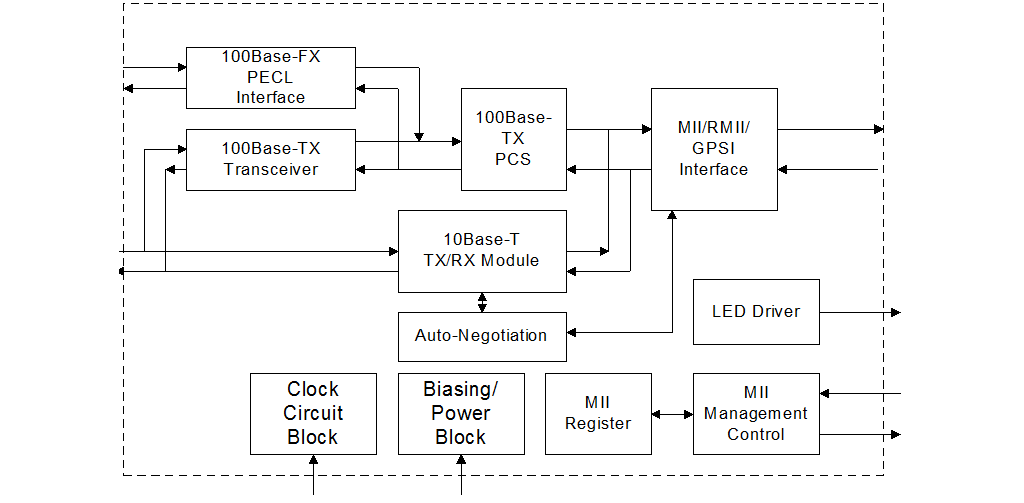

Block Diagram:

interface : MII or RMII (Reduced MII) interface, at he 100BASE-TX

interface : GPSI (7-Wired) or MII mode at the 10Base-T

小結:此類晶片只是一個PHY收發器,屬性是物理層收發器,DM9161AEP通過可變電壓的 MII 或 RMII 標準數字介面連線到 MAC 層,別的晶片提供MAC層。此類晶片選擇主mcu的時候,主mcu必須有MAC控制器。例如:S3C2510(內部含有MAC介面)+DM9161。STM32F4+LAN8720A組合,IMX6+BCM54811也是類似的選擇。

在應用過程中,DM9161AEP常出現的錯誤是,晶振的連線,以及網路變壓器的匹配,所以應該慎重選擇。ETHERNET CONTROLLERS類晶片是PHY+MAC一體的,

ETHERNET CONTROLLERS類晶片是將乙太網媒體接入控制器(MAC)和物理介面收發器(PHY)整合進同一晶片,它包含OSI七層參考模型中第二層資料鏈路層(MAC)和第一層物理層(PHY)。這樣能去掉許多外接元器件。這種方案可使MAC和PHY實現很好的匹配,同時還可減小引腳數、縮小芯片面積;DM9161是物理層介面收發器(PHY),其只包含OSI七層參考模型中的第一層物理層(PHY)。

如果要詳細瞭解此類晶片的使用,可是看STM32F4開發指南-暫存器版本_V1.1裡的第 六十章網路通訊。

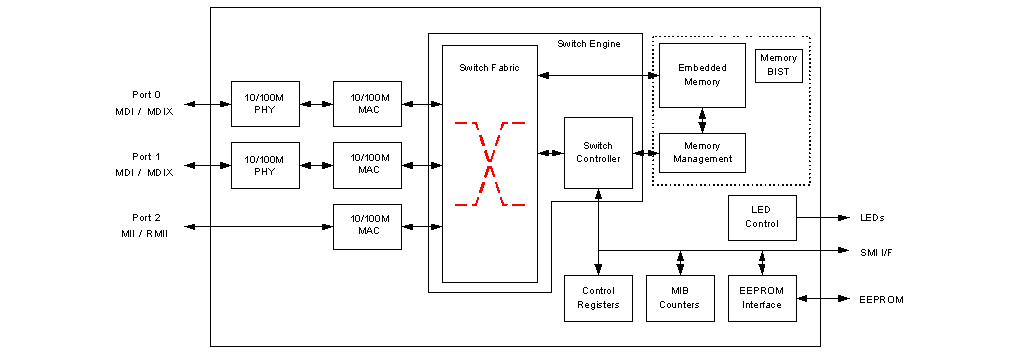

3. SWITCH

The DM8603 is Davicom’s new fully integratedthree-port 10M/100Mbps Fast Ethernet Controller

with Fiber interface. As a fast Ethernet switch,the DM8603 consists of two PHY ports and a third

port with either MII or RMII interface. As theDM8603 was designed with our customers’

requirements in mind, the switch is optimized forhigh performance while being highly

cost-effective.

The two PHY ports on the DM8603 are IEEE 802.3ustandards compliant. Aside for the first two

PHY ports and in an effort for maximum applicationflexibility, the third port on the DM8603 offers

the options to either connect with an MII, reversedMII, or RMII. The reversed MII configuration is

used to connect with SoC’s with a MII interface.The RMII interface is the alternative interface

configuration in case of the need to connect alower pin count Ethernet PHY or SoC.

To maximize the performance of each port, theDM8603 was designed with a number of

features. For proper bandwidth, each port alsosupports ingress and/or egress rate control. In

support of efficient packet forwarding, the DM8603has port-based VLAN with tag/un-tag functions

for up to 16 groups of 802.1Q. Each port includesMIB counters, loop-back capability, built in

memory self test (BIST) for the system, and boardlevel diagnostic.

In designing for the requirements of various data,voice, and video applications, enough internal

memory has been provided for usage of the DM8603’sthree ports, and the internal memory

supports up to 1K uni-cast MAC address table. Thento meet the demands of various bandwidth

and latency issues in data, voice, and videoapplications, each port of the DM8603 has four priority

transmit queues. These queues can be defined eitherthrough port-based operation, 802.1p

VLAN, or the IP packet TOS field automatically.

Block Diagram:

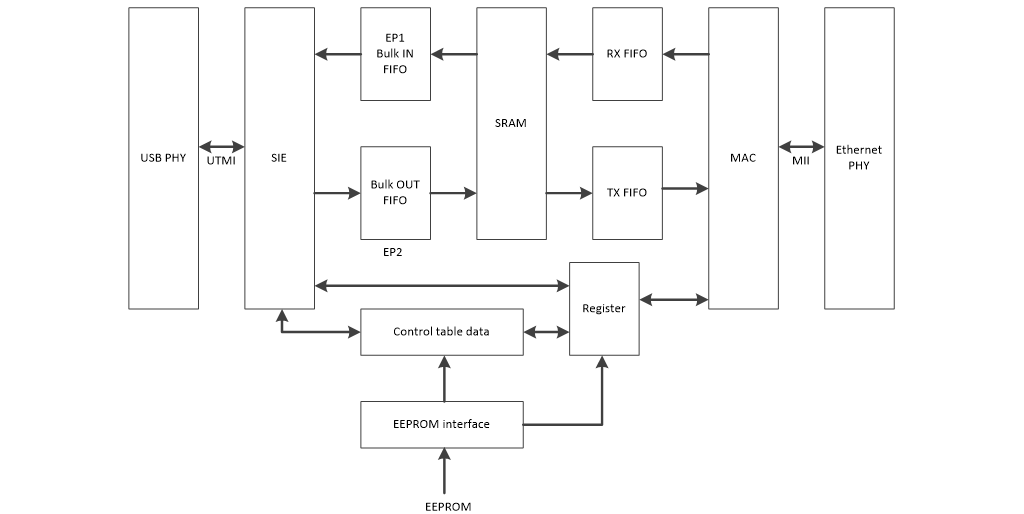

4. USB TO ETHERNET

The DM9620/21 USB to 10/100Mbps Fast Ethernetcontroller is a high performance and highly

integrated ASIC with embedded SSRAM for packetbuffering. It enables low cost and

affordable Fast Ethernet network connection todesktop, notebook PC, and embedded system

using popular USB ports.

It has an USB interface to communicate with USBhost controller and is compliant with USB

specification V1.0, V1.1 and V2.0. It implements10/100Mbps Ethernet LAN function based on

IEEE802.3, and IEEE802.3u standards.

DM9620/21 integrates an on-chip 10/100Mbps EthernetPHY to simplify system design and

provides an optional media-independent interface(MII/RMII/Rev_MII).

Block Diagram:

Certification :

實物: