含PLL的lock訊號的非同步復位同步釋放

阿新 • • 發佈:2019-02-02

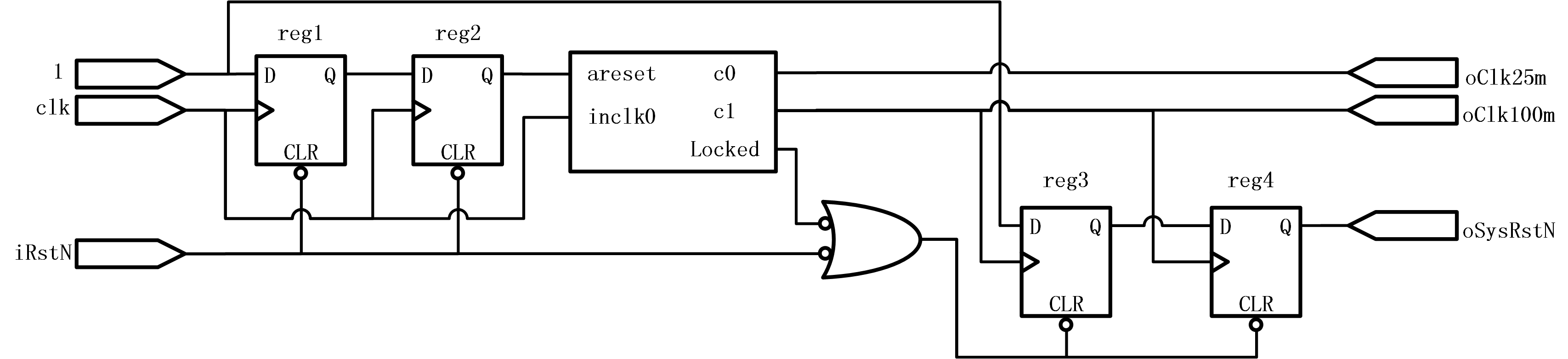

下圖展示了該結構:

結構分為三部分,分別是PLL的非同步復位同步釋放,PLL模組,和系統的非同步復位同步釋放。

PLL模組由IP核產生,使用非同步復位,當鎖定時候,Locked訊號置位。

非同步復位同步釋放部分當iRstN訊號低電平,所有D觸發器輸出0,產生復位訊號;iRstN訊號置位,四個D觸發器都有可能存在亞穩態,使得輸出電平可能為原先電平或者為D端的輸入電平。Reg2與reg4在iRstN置位的瞬間,不管是否亞穩態,則輸出都為低電平,系統仍然處在復位狀態;Reg1和Reg3在iRstN置位的瞬間,若仍為低電平,則經過兩個時鐘後復位輸出為高;若為D埠的輸入,則在一個時鐘後,復位輸出為高。通過兩個D觸發器的緩衝,消除亞穩態的影響。

在系統復位部分,D觸發器的非同步復位輸入端及的是一個閘電路。該閘電路在或門輸入前,將輸入訊號取反,其真值表如下

Lock訊號 | iRstN | 門輸出

--------------------------------------------------------------------

0 | 0 | 1

0 | 1 | 1

1 | 0 | 1

1 | 1 | 0