OV7725攝像頭影象採集基礎知識

目前FPGA用於影象採集 傳輸 處理 顯示應用越來越多,主要原因是影象處理領域的火熱以及FPGA強大的並行處理能力。本文以OV7725為例,對攝像頭使用方面的基礎知識做個小的總結,為後續做個鋪墊。

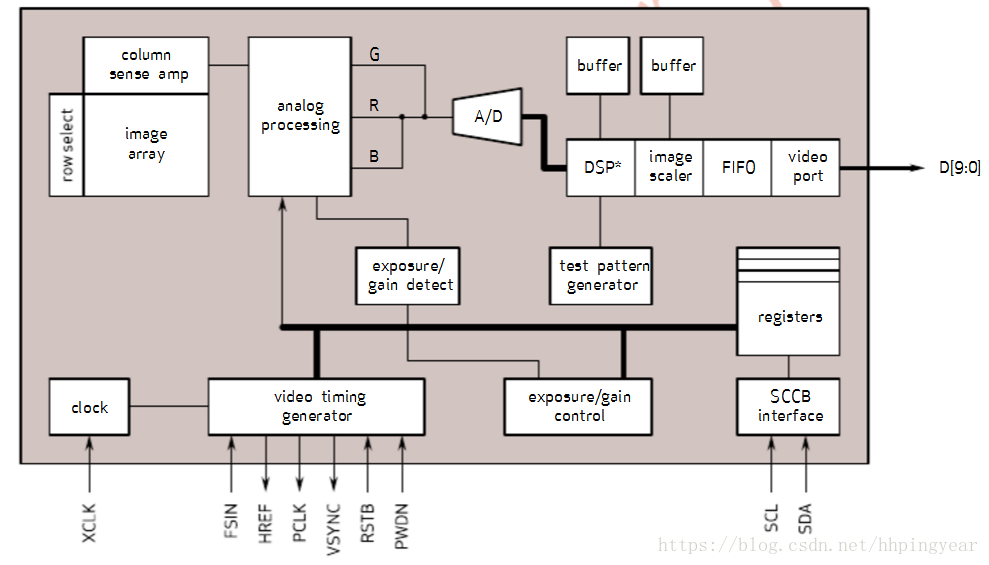

XCLK:工作時鐘輸入,由主控器產生,頻率為24MHz;

HREF:行參考訊號輸出;

PCLK:畫素時鐘輸出,由XCLK產生,用於控制器取樣影象資料(時鐘速率<5ns,);

VSYNC:場同步訊號輸出;

D[9:0] 畫素資料輸出;

RSTB:復位輸入,低電平有效;

PWDN:低功耗模式選擇輸入,正常工作期間需拉低;

SCL:SCCB管理介面時鐘,最高頻率400KHz;

SDA:SCCB介面序列資料匯流排;

PCLK引出一個幀率的概念,單位為fps(Frames Per Second),指每秒鐘輸出幾幅靜態影象,幀率越高視訊越流暢。另外SCCB匯流排與IIC匯流排非常相近,主機寫時序基本一致,故多數影象採集系統直接複用IIC控制器對影象感測器內部暫存器進行配置。這裡給出大體的讀寫流程,具體見參考文獻2。需要格外注意的是,SIO_C時鐘訊號在IDLE狀態下必須為高電平。

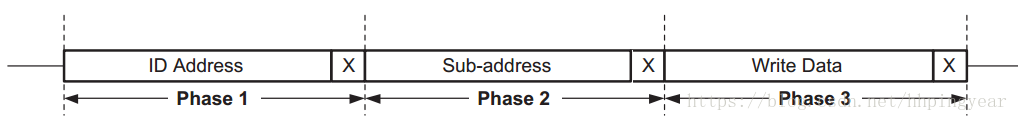

寫操作:

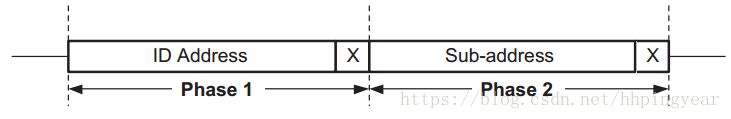

讀操作(分兩部分):

總結來說,SCCB與IIC的主要區別在以下兩點:

1 IIC有重複開始的概念,讀操作先寫裝置地址 再寫暫存器地址,然後重新開始,寫裝置地址,讀取資料。而SCCB讀操作時在第一次寫暫存器地址後必須有結束條件。

2 IIC主機寫資料到從機時,從機必須在寫8bit下一時鐘拉低匯流排響應主機。IIC主機讀取從機資料時,多位元組連續讀取除最後位元組主句均在第9時鐘週期拉低匯流排響應,單位元組讀取拉高匯流排便於下一拍提供停止條件。而SCCB每個phase第9bit為don’t care bit /NACK,主機寫從機第9bit不關心,讀取從機資料由於不支援多位元組操作第9bit主機必須拉高匯流排。

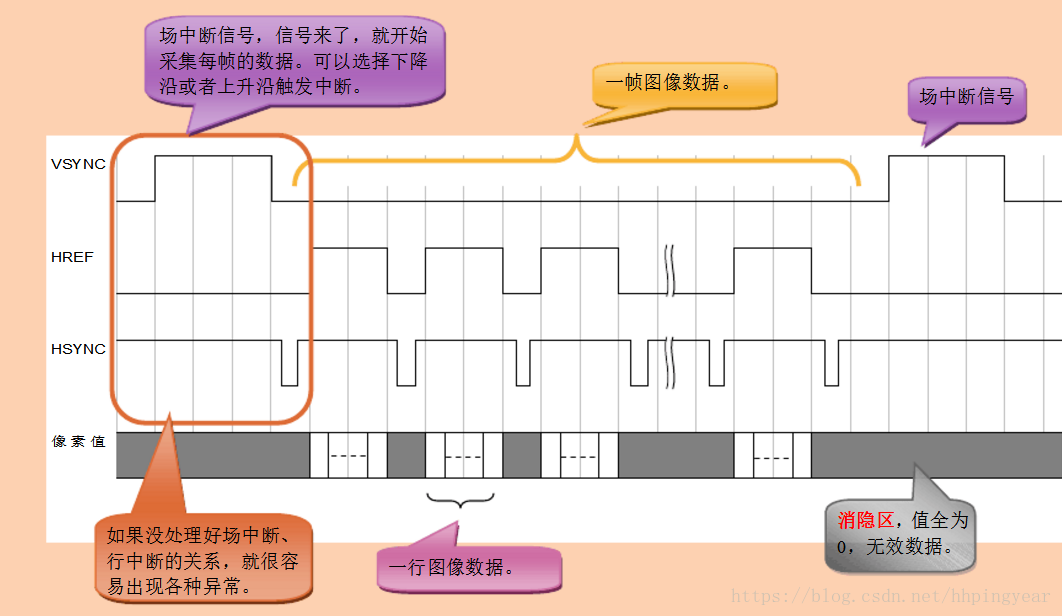

接下來從整體上把握輸出影象資料與同步訊號的關係。(圖片擷取自《OV7725攝像頭程式設計基本知識筆記》,見參考文獻3.

兩個VSYNC高脈衝之間為包含一幀影象資料,但只有HREF高電平期間資料才為有效資料,每個HREF高電平區間對應一行影象資料。因此通過這兩個訊號即可找到有效的影象資料。OV7725攝像頭支援多種影象輸出格式,此處闡述常用的RGB565格式:

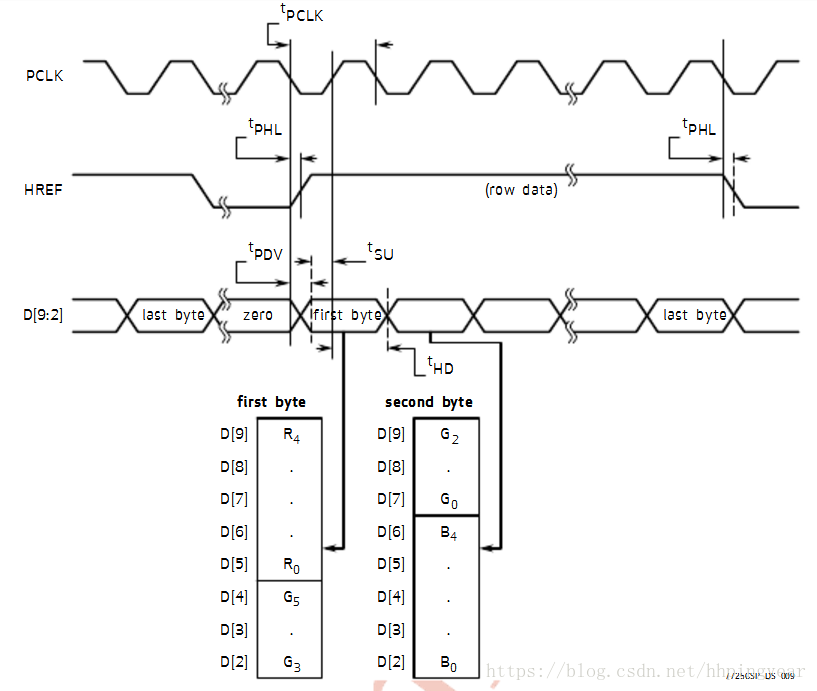

影象資料在PCLK下降沿輸出,控制器在其上升沿取樣。當選擇此模式輸入時,僅使用資料線高八位。時序圖給出了相鄰兩個位元組資料內容,可見兩個位元組表示一個畫素點資料,從高位到低位依次是:R 5bit,G 6bit,B 5bit。Ov7725影象感測器的畫素30萬,解析度:640*480,即每行640個有效畫素點,一共480行。所以每個HREF高脈衝期間有640*2個PCLK週期,兩個VSYNC高脈衝期間迴圈480次。

參考文獻:

1 ov7725手冊(可註釋)圖文

2 OV7725學習之SCCB協議(一) - aslmer - 部落格園 https://www.cnblogs.com/aslmer/p/5965229.html

3 ov7725數字攝像頭程式設計基本知識筆記圖文百度文庫 https://wenku.baidu.com/view/d1af7a731711cc7931b716c6.html