計算機組成原理-實驗三-多功能ALU設計實驗

實驗要求:

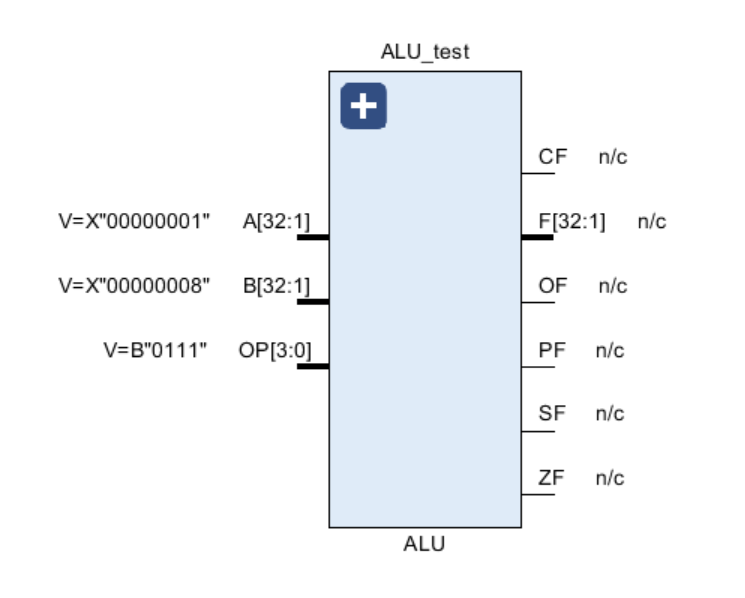

本實驗要求設計一個具有8種運算功能的32位ALU,並能夠產生運算結果的表示:結果為零標誌ZF(Zero Flag)、進借位標誌位CF()溢位標誌OF(Overflow Flag)、符號位標誌SF(Sign Flag)和奇偶標誌PF(Parity Flag),標誌位值解釋見程式碼。ALU通過4根控制線ALU_OP[3:0]來選擇其8種功能,功能見表所示,多餘的8位用於後繼運算的拓展備用。

| ALU_OP[3:0] | ALU功能 | 功能說明 |

| 0000 | and | 按位與運算 |

| 0001 | or | 按位或運算 |

| 0010 | xor | 按位異或運算 |

| 0011 | nor | 按位或非運算 |

| 0100 | add | 算術加運算 |

| 0101 | sub | 算術減運算 |

| 0110 | slt | 若A<B,則輸出1;否則輸出0 |

| 0111 | sll | B邏輯左移A所指定的位數 |

實驗IDE採用Vivado,開發語言Verilog。

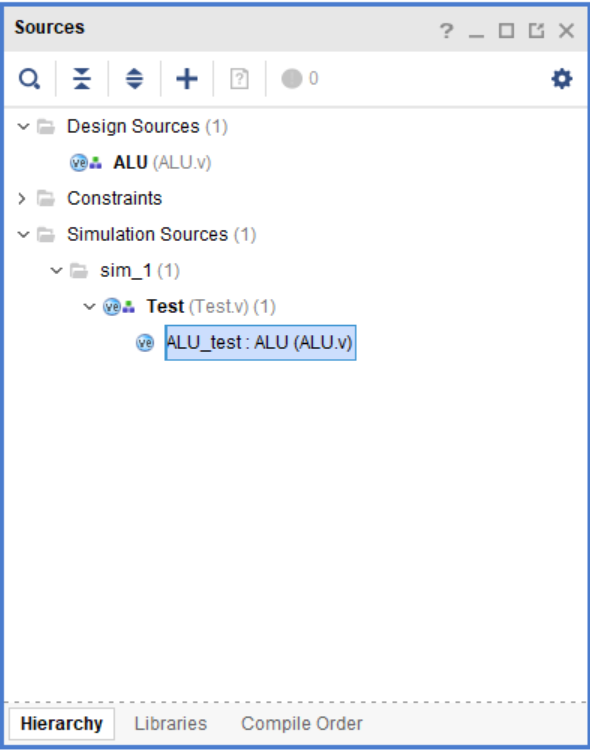

程式模組結構圖:

ALU運算器模組程式碼:

`timescale 1ns / 1ps //ALU模組 module ALU(OP,A,B,F,ZF,CF,OF,SF,PF); parameter SIZE = 32;//運算位數 input [3:0] OP;//運算操作 input [SIZE:1] A;//左運算數 input [SIZE:1] B;//右運算數 output [SIZE:1] F;//運算結果 output ZF, //0標誌位, 運算結果為0(全零)則置1, 否則置0 CF, //進借位標誌位, 取最高位進位C,加法時C=1則CF=1表示有進位,減法時C=0則CF=1表示有借位 OF, //溢位標誌位,對有符號數運算有意義,溢位則OF=1,否則為0 SF, //符號標誌位,與F的最高位相同 PF; //奇偶標誌位,F有奇數個1,則PF=1,否則為0 reg [SIZE:1] F; reg C,ZF,CF,OF,SF,PF;//C為最高位進位[email protected](*) begin C=0; case(OP) 4'b0000:begin F=A&B; end //按位與 4'b0001:begin F=A|B; end //按位或 4'b0010:begin F=A^B; end //按位異或 4'b0011:begin F=~(A|B); end //按位或非 4'b0100:begin {C,F}=A+B; end //加法 4'b0101:begin {C,F}=A-B; end //減法 4'b0110:begin F=A<B; end //A<B則F=1,否則F=0 4'b0111:begin F=B<<A; end //將B左移A位 endcase ZF = F==0;//F全為0,則ZF=1 CF = C; //進位借位標誌 OF = A[SIZE]^B[SIZE]^F[SIZE]^C;//溢位標誌公式 SF = F[SIZE];//符號標誌,取F的最高位 PF = ~^F;//奇偶標誌,F有奇數個1,則F=1;偶數個1,則F=0 end endmodule

測試模組程式碼:

`timescale 1ns / 1ps

module Test();

reg [31:0] A,B;

reg [3:0] OP;

initial//初始化,每中運算擦拭兩組資料

begin

/*按位與*/

OP=4'b0000;A=32'h0000_0000; B=32'h0000_0001;#50;

OP=4'b0000;A=32'h0000_0001; B=32'h0000_0001;#50;

/*按位或*/

OP=4'b0001;A=32'h0000_0000; B=32'h0000_0001;#50;

OP=4'b0001;A=32'h0000_0000; B=32'h0000_0000;#50;

/*按位異或*/

OP=4'b0010;A=32'h0000_0000; B=32'h0000_0001;#50;

OP=4'b0010;A=32'h0000_0000; B=32'h0000_0000;#50;

/*按位或非*/

OP=4'b0011;A=32'h0000_0000; B=32'h0000_0001;#50;

OP=4'b0011;A=32'h0000_0000; B=32'h0000_0000;#50;

/*算術加運算*/

OP=4'b0100;A=32'h7FFF_FFFF; B=32'h7FFF_FFFF;#50;

OP=4'b0100;A=32'hFFFF_FFFF; B=32'hFFFF_FFFF;#50;

/*算術減運算*/

OP=4'b0101;A=32'h7FFF_FFFF; B=32'h7FFF_FFFD;#50;

OP=4'b0101;A=32'h7FFF_FFFF; B=32'hFFFF_FFFF;#50;

/*A<B時,輸出1,否則輸出0*/

OP=4'b0110;A=32'h7FFF_FFFF; B=32'h8FFF_FFFF;#50;

OP=4'b0110;A=32'hFFFF_FFFF; B=32'h7FFF_FFFF;#50;

/*B邏輯左移A指定的位數*/

OP=4'b0111;A=32'h0000_0001; B=32'h0000_0001;#50;

OP=4'b0111;A=32'h0000_0001; B=32'h0000_0008;#50;

end

wire [31:0] F;

wire ZF, CF, OF, SF, PF;

ALU ALU_test(

.OP(OP),

.A(A),

.B(B),

.F(F),

.ZF(ZF),

.CF(CF),

.OF(OF),

.SF(SF),

.PF(PF)

);

endmodule

模擬波形圖:

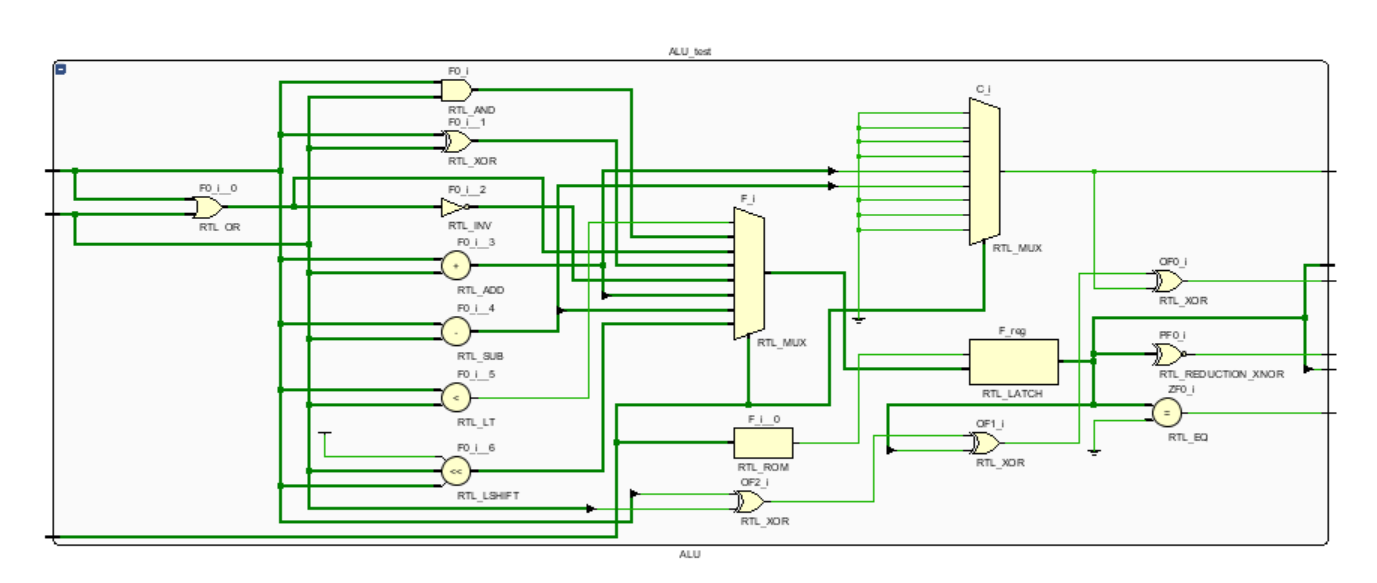

模擬電路圖:

心得體會:

總的來說實驗三不是很難吧,本來書上的要求是做OP[2:0]三位8中運算,標誌位也沒有那麼多。章老師開了翻轉課堂,給我們加了一些要求。這是本學期我們的第一個實驗,很多Verilog的語法都忘記了,磕磕碰碰和組員討論,debug。非常感謝另外兩個小夥伴lym和tk。

相關推薦

計算機組成原理-實驗三-多功能ALU設計實驗

實驗要求: 本實驗要求設計一個具有8種運算功能的32位ALU,並能夠產生運算結果的表示:結果為零標誌ZF(Zero Flag)、進借位標誌位CF()溢位標誌OF(Overflow Flag)、符號位標誌SF(Sign Flag)和奇偶標誌PF(Parity Fl

計算機組成原理(三)儲存器的層次結構

組成原理(三)儲存器的層次結構 第三章 儲存器的層次結構 3.1 儲存器分類 按儲存介質分類 (1)半導體儲存器: &

計算機組成原理補充——三種重新整理方式,存取週期>存取時間的原因

常見的動態RAM的共同特點是都靠電容儲存電荷的原理來寄存資訊,電容上的電荷一般只能維持1~2ms,因此即使電源不掉電,資訊也會自動消失,所以必須在2ms內對其所有儲存單元恢復一次原狀態,稱為重新整理,重新整理是一行一行進行的。又因為記憶體就一套地

重學計算機組成原理(三)- 進擊,更強的效能!

在上一篇中,我們談到過 程式的CPU執行時間 = 指令數×CPI×Clock Cycle Time 要提升計算機的效能,可以從上面這三方面著手。 通過指令數/CPI,好像都太難了。 因此工程師們,就在CPU上多放電晶體,不斷提升CPU的時鐘頻率,讓CPU更快,程式的執行時間就會縮短。 從1978年I

華中科技大學 計算機組成原理 上機實驗1 2018

image 可能 ive debug 區號 分析 pan open 實驗目的 實驗目的 GB2312 區位碼 字模碼 奇偶校驗校 驗位 檢錯 海明碼編解碼電路基本原理 流水數據傳輸機制,流水暫停原理 實驗環境 (以下文字僅

計算機組成原理補充——多體並行:高位/低位交叉編址

(1)圖是適合於並行工作的高位交叉編址的多體儲存器結構示意圖,圖中程式因按體內地址順序存放(一個體存滿後,再存入下一個體),故又有順序儲存之稱。高位地址可表示體號,低位地址為體內地址。按這種編址方式,只要合理調動,使不同的請求源同時訪問不同的體,便可

學習彙集地,如果你擅長計算機組成原理,多執行緒,設計模式,jvm,前端或者其他都可以

擅長jvm 多執行緒 設計模式 資料庫 前端 分散式什麼的一起學習共同進步。 目的是大家在自學新的領域的時候有地方可以探討求疑 比如在看到垃圾回收各種收集器中遇到執行緒方面知識的時候 學習設計模式分不清單例和享元的區別,只有書本經驗不知道如何應用到實際開發的時候 學習資料庫系統

計算機組成原理實驗2---單週期CPU

實驗目的 實驗內容 設計一個單週期CPU,該CPU至少能實現以下指令功能操作。 必須寫一段測試用的彙編程式,而且必須包含所要求的所有指令,slti指令必須檢查兩種情況:“小於”和“大於等於”;beq、bne:“不等”和“等”。這段彙編程式必須儘量優化且出現在實驗報告中,同時,給出每條指令

計算機組成原理實驗之運算器組成實驗

一、實驗目的: 1、熟悉邏輯測試筆的使用方法; 2、熟悉LK-TEC-9模型計算機的節拍脈衝T1、T3、T3; 3、熟悉雙埠通用暫存器組的讀寫操作; 4、熟悉運算器的資料傳送通路; 5、驗證74LS181的加、減、與、或功能; 6、按給定的資料,完成幾種指定的

計算機組成原理實驗之 雙埠儲存實驗(LK-TEC-9)

一、實驗目的: 1、瞭解雙埠靜態儲存器IDT7132的工作特性及其使用方法; 2、瞭解半導體儲存器怎樣儲存和讀取資料; 3、瞭解雙埠儲存器怎樣並行讀寫; 4、熟悉LK-TEC-9模型計算機儲存器部分的資料通路; 5、掌握資料通路中各個控制訊號的作用和用法; 6

計算機組成原理筆記-第三章(哈工大)

1.匯流排的基本概念 匯流排:是連線各個部件的資訊傳輸線,是各個部件共享的傳輸介質。 匯流排的傳輸方式: 序列——長距離 ,一次傳輸1位 並行——短距離,一次傳輸n位 2.匯流排分類 1.片內匯流排 晶片內部的匯流排

計算機組成原理——cpu的簡單模型實驗報告

#cpu與簡單模型機 姓名: 學號: 班級:計科班 實驗名稱:CPU與簡單模型機 實驗性質:綜合型實驗 時間:2018.12.1 一、實驗目的 (1) 掌握一個簡單 CPU 的組成原理。 (2) 在掌握部件單元電路的基礎上,進一步將其構造一

計算機組成原理(1)實驗3

一. 運算器實驗 1.實驗內容及要求 1) 讀出系統已有的微指令,並理解其含義。 2) 設計並實現微指令系統。 3) 瞭解譯碼器、微指令結構的基本工作原理。 4) 學習設計微指令的方法。 2.實驗環境 DICE-CP266計算機組成原理與系統

計算機組成原理實驗二:RAM實驗

一、實驗專案名稱:RAM實驗 二、實驗目的: 瞭解半導體靜態隨機讀寫儲存器RAM的工作原理及其使用方法。 掌握半導體儲存器的字、位擴充套件技術。 三、實驗內容 ◆採用1K x 4 的晶片,構成1K x 8的儲存器。 ◆選擇五個不連續的存貯單元地址,分別存入不同內容

計算機組成原理實驗四

上機實驗04 邏輯運算程式設計實驗1.瞭解組合語言的邏輯運算指令; 2.熟悉組合語言中邏輯運算指令的使用方法; 3.掌握利用匯編語言邏輯運算指令實現程式設計的方法。二、軟硬體環境 1.硬體環境:微機CPU 486以上,500MB以上硬碟,32M以上記憶體; 2.軟體環境:

計算機組成原理三:匯流排

第三章:匯流排 1)匯流排概念: 計算機硬體系統有2種互聯方式,一種是各部件之間單獨連線,稱為分散連線;另一種是將各部件連到一組公關資訊 傳輸線上,稱為匯流排連線.匯流排是一組線路,將計算機的各個硬體連線在一起,讓它們可以通過這條公共線路進行資料的傳輸. 2

計算機組成原理實驗:乘法實現

1、實驗目的:開放性實驗,根據原理圖實現乘法的電路設計並執行。2、實驗原理:原理一:如圖3-1是實現原碼一位乘運算的基本硬體配置框圖,根據該圖用移位相加方法實現乘法,自行選擇器件設計電路並執行。圖3-1

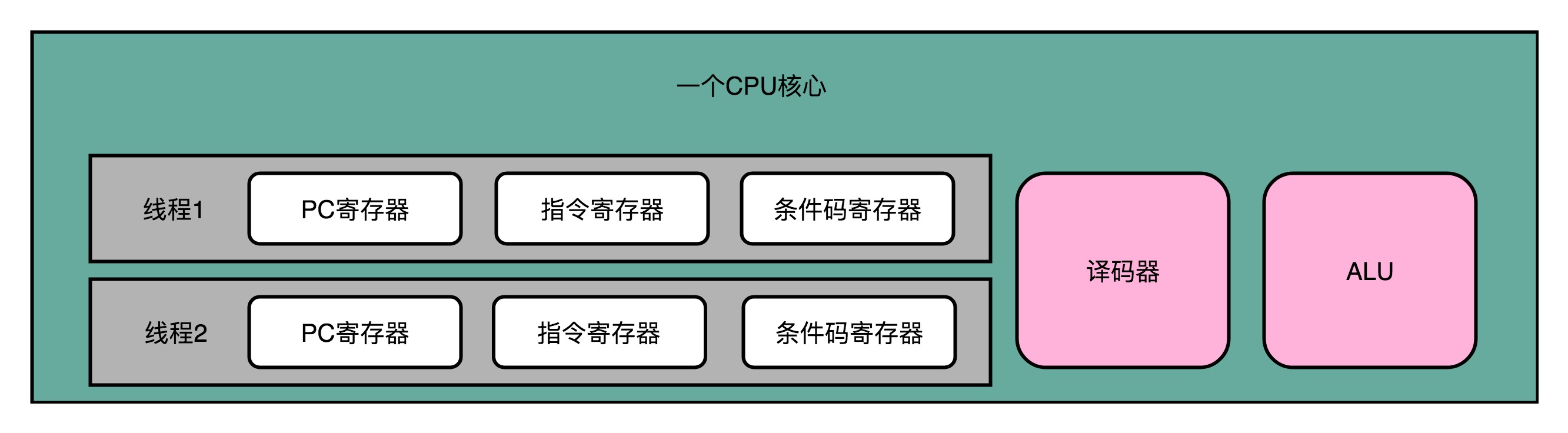

計算機組成原理筆記(三)

我的部落格 : https://www.luozhiyun.com/ ## 超執行緒  超執行緒的CPU,其實是把一個物

python 學習day1--計算機組成原理

編程 系統 height 保持 次數 電腦 但是 col 存儲 1. Python是一款編程語言,用於程序員與計算機的溝通,即程序員可以通過編程讓計算機實現某些特定功能。 用程序語言開發程序,最終開發出的是一個軟件,目前我們使用的軟件均是需要運行在操作系統之上的,我了解到之

計算機組成原理

橋梁 ros 設備 程序員 行數 找到 存儲系統 部件 找文件 計算機組成原理內容如下: 一、編程語言的作用及與操作系統和硬件的關系 1、編程語言是程序員與計算機溝通的介質,從字面上可以看出它是一種語言,我們平常也會使用語言去交流。 然而只有編程語言和硬件是不行的,