鎖相環PLL(Phase Locked Loop)

鎖相環PLL

目前我見到的所有晶片中都含有PLL模組,而且一直不知道如何利用PLL對晶振進行倍頻的,這次利用維基百科好好的學習了下PLL的原理。

1. 時鐘與振盪電路

在晶片中,最重要的就是時鐘,時鐘就像是心臟的脈衝,如果心臟停止了跳動,那人也就死亡了,對於晶片也一樣。瞭解了時鐘的重要性,那時鐘是怎麼來的呢?時鐘可以看成周期性的0與1訊號變化,而這種週期性的變化可以看成振盪。因此,振盪電路成為了時鐘的來源。

振盪電路的形成可以分兩類:

1. 石英晶體的壓電效應:電導致晶片的機械變形,而晶片兩側施加機械壓力又會產生電,形成振盪。它的諧振頻率與晶片的切割方式、幾何形狀、尺寸有關,可以做得精確,因此其振盪電路可以獲得很高的頻率穩定度。

2. 電容Capacity的充電放電:能夠儲存電能,而充放電的電流方向是反的,形成振盪。可通過電壓等控制振盪電路的頻率。

2. PLL與倍頻

由上面可以知道,晶振由於其頻率的穩定性,一般作為系統的外部時鐘源。但是晶振的頻率雖然穩定,但是頻率無法做到很高(成本與工藝限制),因此晶片中高頻時鐘就需要一種叫做壓控振盪器(Voltage Controlled Oscillator)的東西生成了(顧名思義,VCO就是根據電壓來調整輸出頻率的不同)。可壓控振盪器也有問題,其頻率不夠穩定,而且變化時很難快速穩定頻率。哇偶,看到這種現象是不是很熟悉?嘿嘿,這就是標準開環系統所出現的問題,解決辦法就是接入反饋,使開環系統變成閉環系統,並且加入穩定的基準訊號,與反饋比較,以便生成正確的控制。

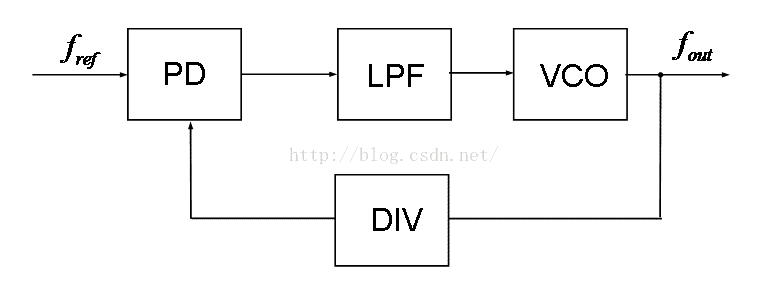

PLL倍頻電路

因此,為了將頻率鎖定在一個固定的期望值,鎖相環PLL出現了!一個鎖相環PLL電路通常由以下模組組成:

· 鑑相鑑頻器PFD(Phase Frequency Detector):對輸入的基準訊號(來自頻率穩定的晶振)和反饋迴路的訊號進行頻率的比較,輸出一個代表兩者差異的訊號

· 低通濾波器LPF(Low-Pass Filter):將PFD中生成的差異訊號的高頻成分濾除,保留直流部分

· 壓控振盪器VCO(Voltage Controlled Oscillator):根據輸入電壓,輸出對應頻率的週期訊號。利用變容二極體(偏置電壓的變化會改變耗盡層的厚度,從而影響電容大小)與電感構成的LC諧振電路構成,提高變容二極體的逆向偏壓,二極體內耗盡層變大,電容變小,LC電路的諧振頻率提高,反之,降低逆向偏壓時,二極體內電容變大,頻率降低

· 反饋迴路FL(Feedback Loop):通常由一個分頻器實現。將VCO的輸出降低到與基準訊號相同級別的頻率才能在PFD中比較

PLL工作的基本原理就是將壓控振盪器的輸出經過分頻後與基準訊號輸入PFD,PFD通過比較這兩個訊號的頻率差,輸出一個代表兩者差異的訊號,再經過低通濾波器轉變成一個直流脈衝電壓去控制VCO使它的頻率改變。這樣經過一個很短的時間,VCO的輸出就會穩定下來。所以:

PLL並不是直接對晶振進行倍頻,而是將頻率穩定的晶振作為基準訊號,與PLL內部振盪電路生成的訊號分頻後進行比較,使PLL輸出的訊號頻率穩定

最後,根據原理,理解一下鎖相環(Phase Locked Loop)的名稱

· 為了對基準訊號與反饋訊號進行頻率比較,二者的相位必須相同且鎖住,任何時間都不能改變,這樣才能方便的比較頻率,所以叫鎖相(Phase Locked)

· 為了快速穩定輸出系統,整個系統加入反饋成為閉環,所以叫環(Loop)

轉自:http://joeshang.github.io/2014/03/27/understand-pll/