PLL與DLL鎖相環介紹

一、PLL鎖相環:Phase-Locked Loop

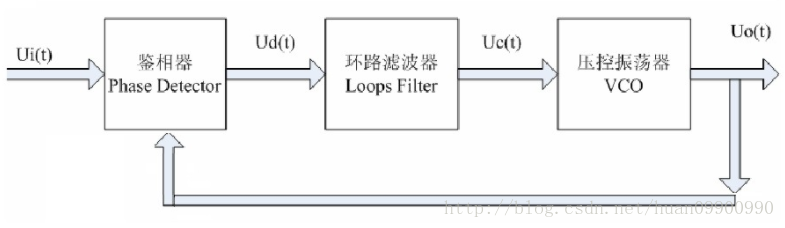

由鑑相器、環路濾波器和壓控振盪器組成,鑑相器用來鑑別輸入訊號Ui與輸出訊號Uo之間的相位差,並輸出誤差電壓Ud。Ud中的噪聲和干擾成分被低通性質的環路濾波器濾除。形成壓控振盪器(Vco)的控制電壓Uc,Uc作用於壓控振盪器的結果是把它的輸出震盪頻率fo拉向環路輸入訊號頻率fi,當二者相等時,環路被鎖定,稱為入鎖。PLL並不是直接對晶振進行倍頻,而是將頻率穩定的晶振作為基準訊號,與PLL內部振盪電路生成的訊號分頻後進行比較,使PLL輸出的訊號頻率穩定,工作原理如下圖所示。

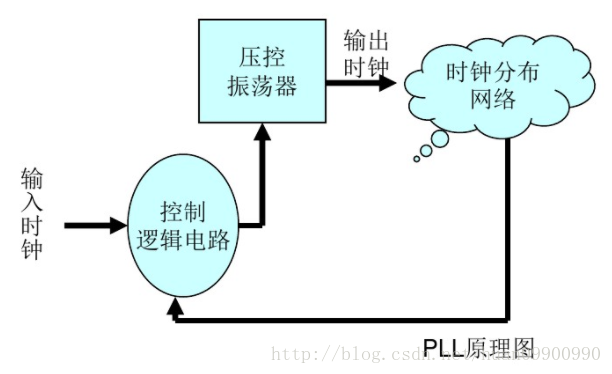

下圖是另一種PLL原理圖,控制電路由上圖的鑑相器和環路濾波器組成,調整振盪器的頻率和相位就可以補償時鐘分佈造成的時間延遲。

PLL有 以下幾個顯著特點:

(1)輸出時鐘是內部VCO自振產生的,把輸入參考時鐘和反饋時鐘的變化轉換為電壓訊號間接地控制VCO的頻率;

(2)VCO輸出頻率有一定的範圍,如果輸入時鐘頻率超出這個頻率,則鎖相環不能鎖定;

(3)LPF部件可以過濾輸入時鐘的高頻抖動,其輸出時鐘的抖動主要來自VCO本身及電源噪聲,而不是輸入時鐘帶入的抖動;

(4)由於是類比電路,因此對電源噪聲敏感,在設計PCB時,一般需要單獨的模擬電源和模擬地。

二、DLL鎖相環

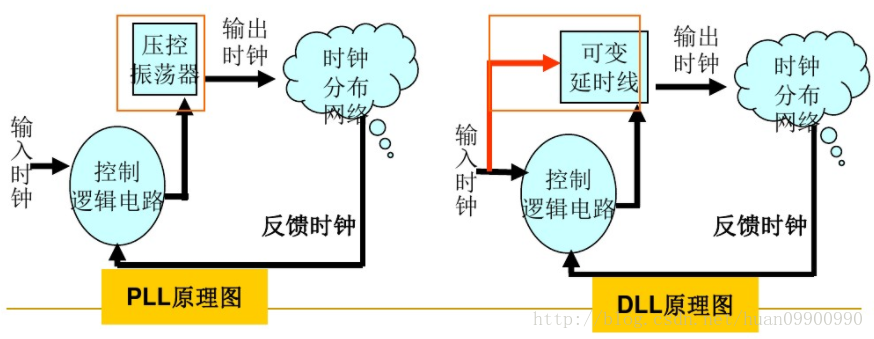

DLL是基於數字抽樣方式,在輸入時鐘和反饋時鐘之間插入延遲,使輸入時鐘和反饋時鐘的上升沿一致來實現的。又稱數字鎖相環。一個最簡單的DLL與PLL的主要不同在於DLL用延時線代替了PLL的壓控振盪器,延時線產生輸入時鐘的延時輸出。時鐘分佈網路把時鐘送到內部暫存器的時鐘埠,控制邏輯對輸入時鐘和反饋時鐘進行抽樣、比較,調整延時線。兩者的實現方式如下圖所示。

DLL就是在輸入時鐘和反饋時鐘間插入延時脈衝,直到這兩個時鐘上升沿對齊達到同步,DLL才能鎖定。這樣兩個時鐘沒有了差別,也就補償了時鐘分配網路造成的時間延時,有效改善了時鐘源和負載之間延時。

DLL的典型特徵如下:

(1)時鐘輸出真實、及時地反映輸入時鐘,跟蹤輸入時鐘迅速;

(2)能鎖定的輸入時鐘頻率範圍較寬,但是由於延時電路的總延時有限,因此不能鎖定時鐘頻率過低的輸入時鐘;

(3)不能過濾時鐘源的抖動,會引入固有抖動,造成抖動的累計;

(4)用數位電路實現,對電源噪聲不敏感。

三、PLL與DLL

兩者功能上都可以實現倍頻、分頻、佔空比調整,但是PLL調節範圍更大,比如說:XILINX使用DLL,只能夠2、4倍頻;ALTERA的PLL可以實現的倍頻範圍就更大畢竟一個是模擬的、一個是數字的。

DLL數位電路與PLL類比電路實現時有精確的時序,而數位電路實現時:抗噪聲,低功耗,抗抖動,移植性好。

PLL的振盪器有不穩定,相位偏移的積累而DLL技術穩定,沒有累計相位偏移。因而在延時補償和時鐘調整時常用DLL。