Xilinx FPGA 學習筆記——時鐘資源

在Xilinx的FPGA中,時鐘網路資源分為兩大類:全域性時鐘資源和區域時鐘資源。

全域性時鐘資源是一種專用互連網路,它可以降低時鐘歪斜、佔空比失真和功耗,提高抖動容限。Xilinx的全域性時鐘資源設計了專用時鐘緩衝與驅動結構,從而使全域性時鐘到達CLB、IOB和BRAM的延時最小。

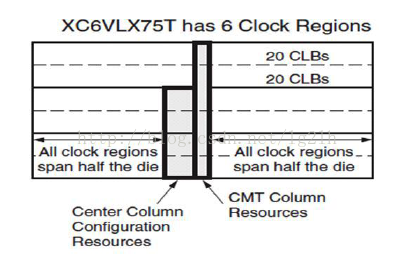

區域時鐘資源是獨立於全域性時鐘網路的。Xilinx的器件分成若干個時鐘區域,以Virtex-6為例,Virtex-6的最小器件有6個區域,最大器件有18個區域。它與全域性時鐘不同,區域時鐘訊號X只能驅動限定的時鐘區域。

這裡面提到區域時鐘的概念,需要解釋一下。Xilinx的FPGA器件是通過時鐘區域來管理時鐘網路的,以

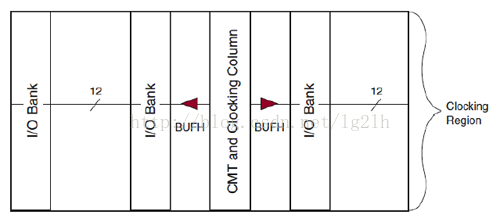

每個時鐘區域的中間方向有一個時鐘行(HROW),以Virtex-6為例,一個時鐘行,共包含12個水平時鐘線,12個水平時鐘線可以全部由全域性時鐘BUFG驅動。也可以由區域內部的時鐘元件緩衝器驅動,例如BUFH和BUFR。這個時候有人會問什麼是BUFG、BUFR和BUFH。

先來解釋一下BUFG,這個比較簡單,就是全域性時鐘網路時鐘驅動器,如果時鐘訊號要走全域性時鐘網路,必須通過這個BUFG來驅動,BUFG可以驅動所有的CLB,RAM,IOB。spartan6 有一共有16個BUFG全域性時鐘線

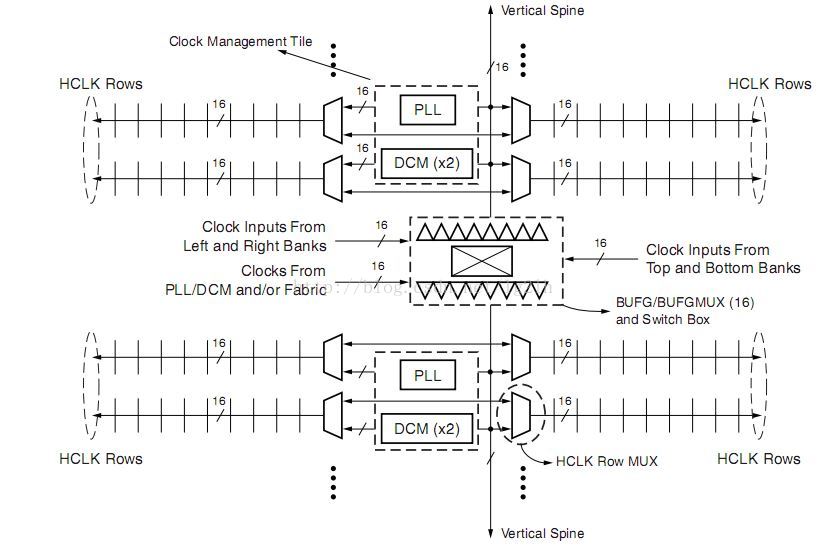

再看BUFH,BUFH驅動區域中的水平全域性時鐘樹,Xilinx的時鐘是通過時鐘樹來分佈的,以spartan6時鐘樹為例,看下圖。FPGA中間豎排是CMT時鐘管理模組,就是PLL和DCM。全域性時鐘緩衝器BUFG是位於FPGA器件的中心位置,時鐘的輸入可以來自FPGA的上、下、左、右的bank,也可以來自PLL或DCM;16個BUFGMUX通過驅動vertical

spine並經vertical spine 往南北方向傳播,vertical spine就相當於時鐘樹的樹幹 ,根據這條線路,時鐘水平延伸至HCLK時鐘列並經HCLK時鐘列提供了訪問區域性邏輯原語的路徑,HCLK及所謂的水平時鐘線,相當於樹枝

以Virtex-6每一個HCLK列左右兩邊各有12個水平時鐘緩衝BUFH驅動左右邏輯資源,即每個時鐘區域有12個BUFH時鐘線。如下圖

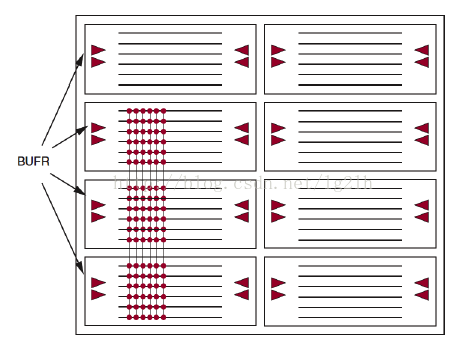

最後解釋BUFR,BUFR我在SPARTAN6的時鐘資源手冊UG382裡沒有看到,應該是沒有啊。BUFR是區域時鐘緩衝器,要進入區域時鐘網路,必須例化BUFR。一個BUFR最多可以驅動三個相鄰的時鐘區域中的區域時鐘。頂部和底部區域中BUFR只能連線相鄰的一個時鐘區域,也就是說,頂部的BUFR連線它所在的下面一個相鄰區域。底部的BUFR只能連線它所在的上邊一個相鄰區域。因此,底部和頂部BUFR的作用區域為兩個時鐘區域。如下圖,下圖是共有8個時鐘區域的FPGA,每個時鐘區域最多包含6個BUFR時鐘線。截止現在可以看到(紫色標註)Vertex器件的每個時鐘區域,共有6個BUFR和12個BUFH。SPARTAN6每個時鐘區域好像就有16個BUFH。最後宣告一下BUFR不僅可以驅動IO,也可以驅動CLB,RAM。下面接收的BUFIO只能驅動IOB模組。BUFR還可以1-2-4-8分頻。

最後說一下BUFIO,BUFIO是用來驅動I/O列內的專用時鐘網路,這個專用的時鐘網路獨立於全域性時鐘資源,適合採集源同步資料。BUFIO只能由位於同一時鐘區域的Clock-Capable I/O驅動。一個時鐘區域有4個BUFIO,其中的2個可以驅動相鄰區域的I/O時鐘網路。BUFIO不能驅動邏輯資源(CLB、BRAM等),因為I/O時鐘網路只存在於I/O列中。

具體這些個時鐘元件BUF怎麼用,我還沒實踐,先對這些BUF概念理解一下,僅供大家參考。小弟初學,肯定有理解不對的地方,大家請指正。

參考文獻的連結:

http://xilinx.eetrend.com/blog/1957

http://blog.sina.com.cn/s/blog_bff0927b010173bp.html

http://www.tools138.com/front/article/queryById.htm?id=417885