單週期cpu設計程式碼解讀

阿新 • • 發佈:2019-05-29

目錄

- 寫在前面

- 單週期cpu設計程式碼講解

- 概念回顧

- Verilog程式碼講解

寫在前面

歡迎轉載,轉載請說明出處。

單週期cpu設計程式碼講解

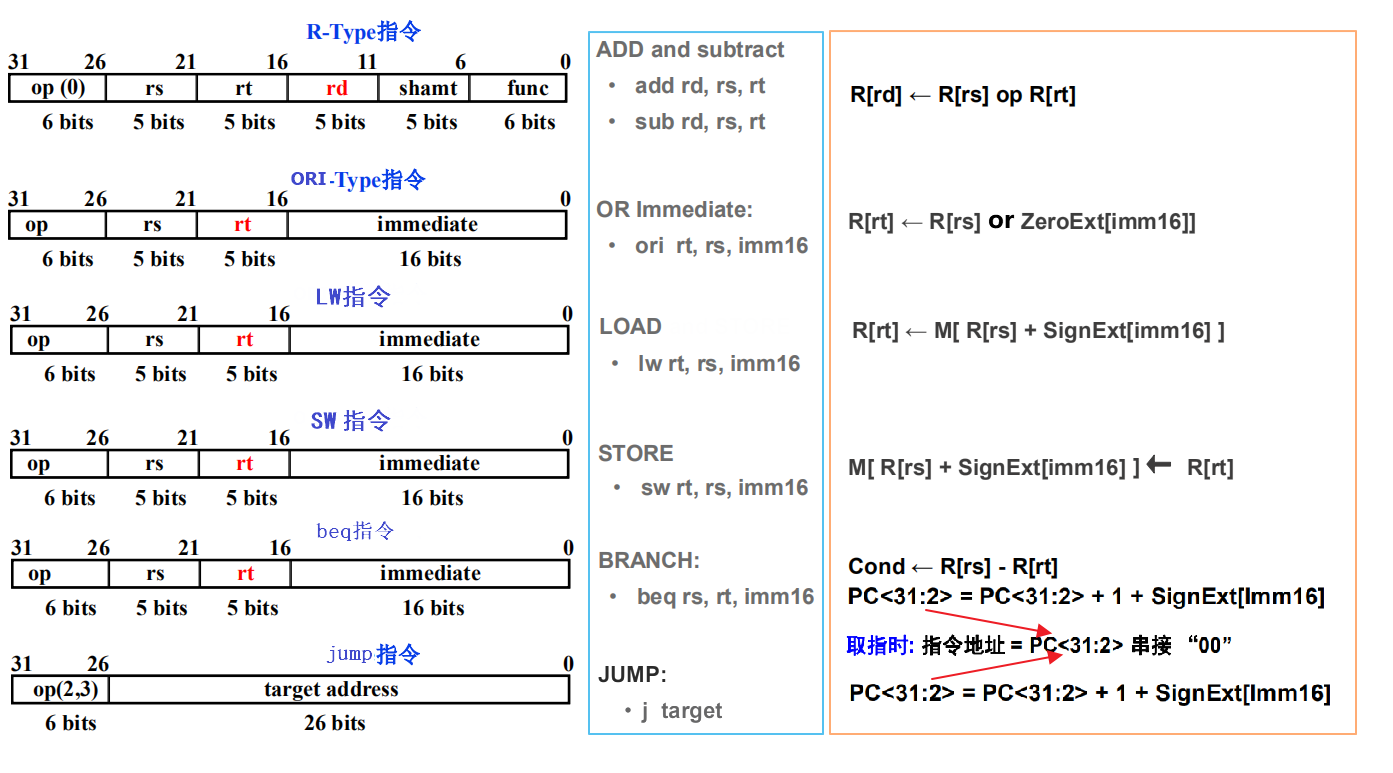

概念回顧

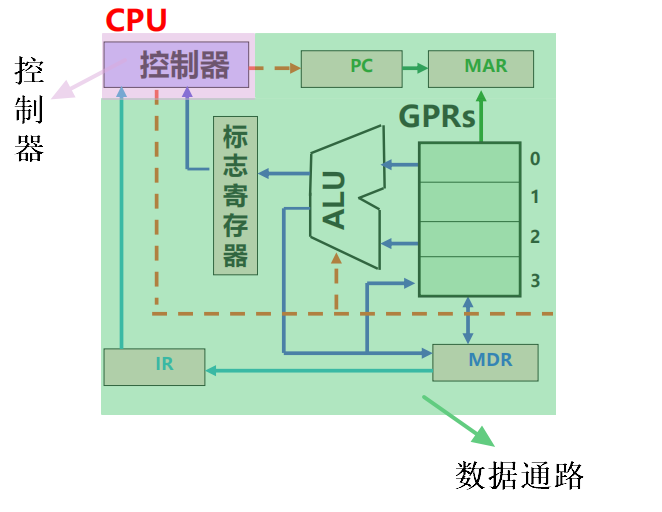

一、電子計算機的部件

分為:中央處理器(cpu)、內部儲存器(Memory)、輸入/輸出(I/O)裝置,以及連線它們的匯流排(Bus)。下圖為圖示,注意色塊的區分。

二、cpu

又包括控制器(Controller)和資料通路(Data Path)。下圖為圖示,注意色塊區分。

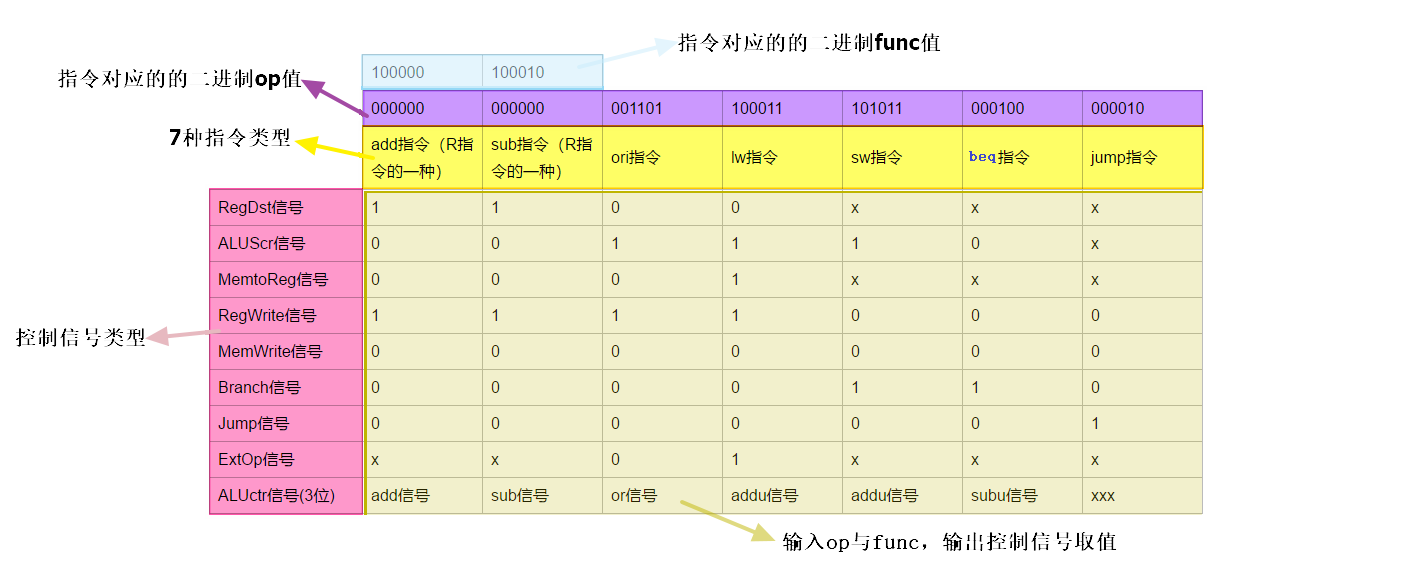

三、控制器

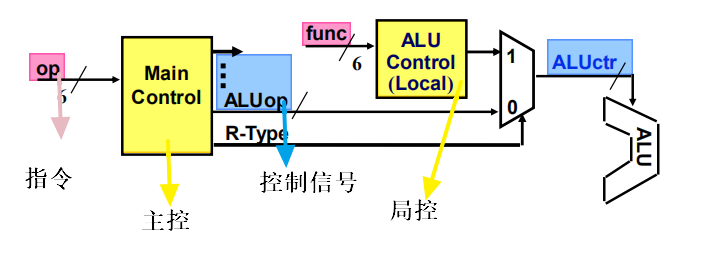

分為主控(Main Control)和局控(Local Control或ALU Control)。將二進位制指令輸入控制器,生成控制訊號,該過程稱為譯碼。控制訊號控制資料通路工作。且不同的指定對應不同的控制訊號。

下圖為在控制器中譯碼的邏輯示意圖:

下圖為在控制器中譯碼的物理示意圖:

講解一下從邏輯圖到物理圖的轉換:

- 首先由主控解析op指令,如果發現該指令為“000000”則表示該指令是R指令,輸出中間訊號R-Type為1,否則為0;如果發現該指令是其他值,則按照邏輯圖,為RegDst等訊號賦相應的值;

- 中間訊號R-Type起到二路選擇的作用,如圖。

- 中間訊號ALUop,在R-Type為0(選擇0路)時,直接通過局控,輸出成為ALUctr訊號,對應上面邏輯圖的最後一行後5列;在R-Type為1時,局控起作用。

- 局控解析R指令的func部分,輸出對應指令的ALUctr訊號。

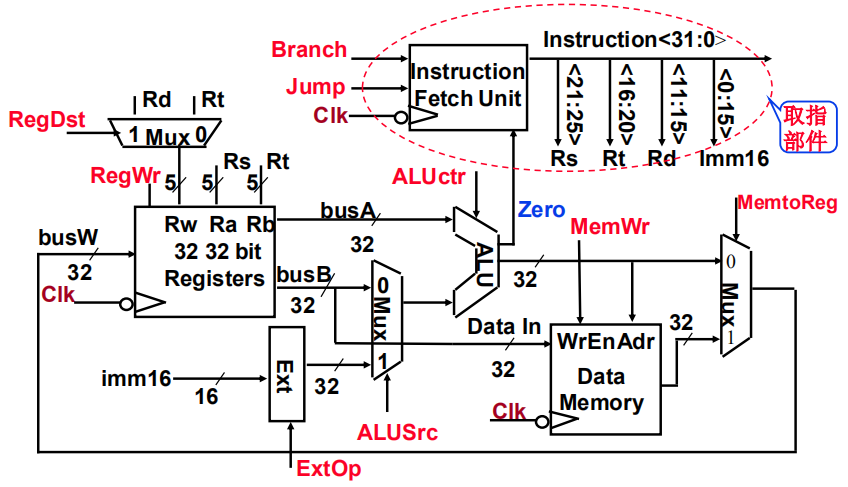

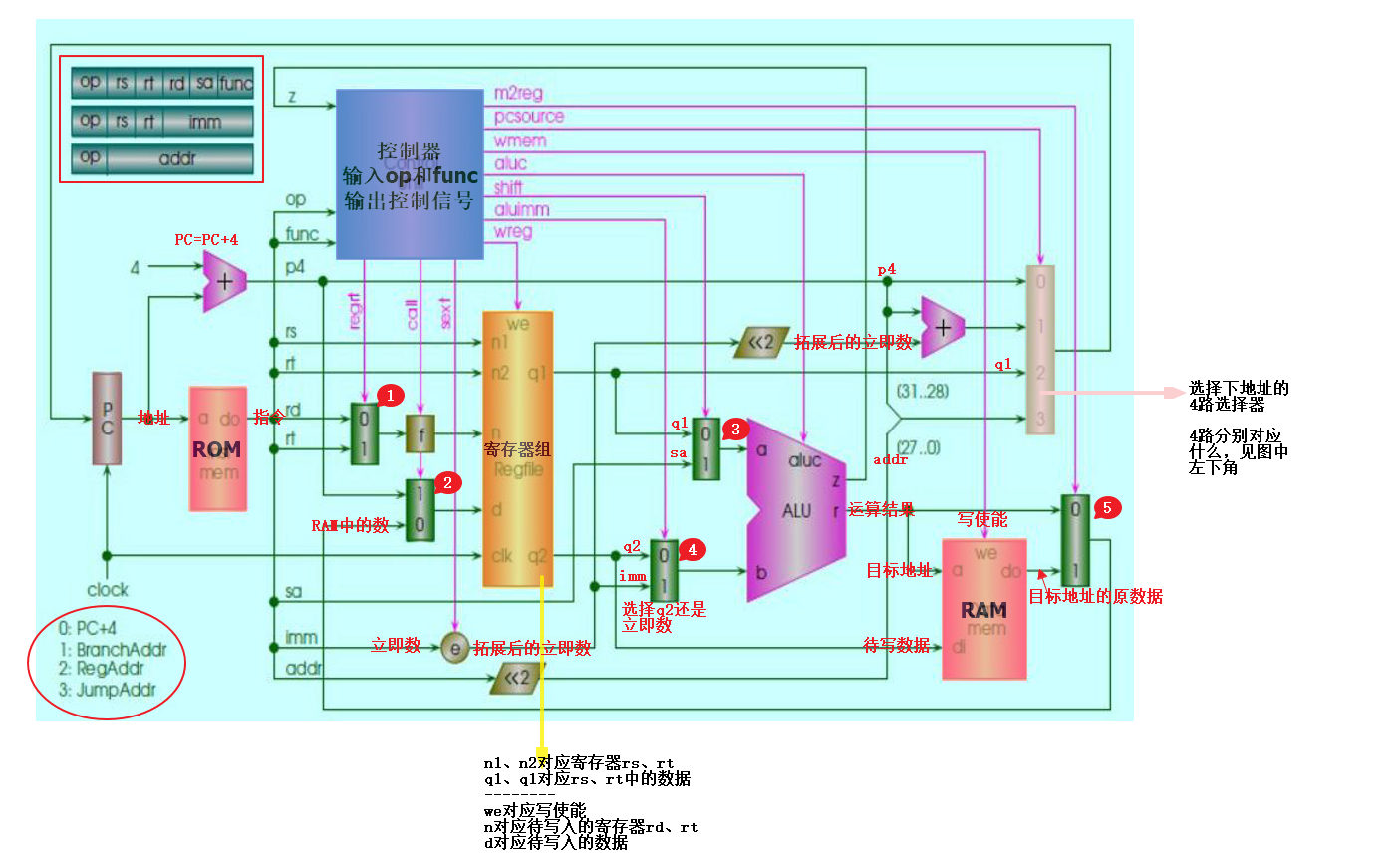

四、資料通路:

是包括運算器、暫存器組、儲存器(快取記憶體)、多路選擇器等等在內的元件的有結構的組合。如下圖所示:

【資料通路各部分的講解將結合程式碼完成】

Verilog程式碼講解

在程式碼講解之前有必要放幾張圖:

shift.v

/*移位*/ /*輸入一個數,返回移位之後的結果*/ /*輸入d(待移的數)、sa(移動的位數)、right(移動方向)、arith(空位補全方式)*/ /*輸出sh(移位後的結果)*/ module shift (d,sa,right,arith,sh); input [31:0] d; input [4:0] sa; input right,arith; output [31:0] sh; reg [31:0] sh; // 組合邏輯 always @* begin if (!right) begin // right為邏輯0時,左移 sh = d << sa; end else if (!arith) begin // right為邏輯1,且arith為邏輯0時,右移、0補空 sh = d >> sa; end else begin // 右移、1補空 sh = $signed(d) >>> sa; end end endmodule

scinstmem.v

/*從ROM(只讀儲存器)讀資料*/

/*輸入目標資料在ROM中的地址a*/

/*輸出地址對應的資料inst*/

module scinstmem (a,inst);

input [31:0] a;

output [31:0] inst;

wire [31:0] rom [0:31]; // 定義32個32位的儲存器ROM

// 想ROM中寫入一組指令,指令對應的彙編含義見行註釋

assign rom[5'h00] = 32'h3c010000; // (00) main: lui r1,0

assign rom[5'h01] = 32'h34240050; // (04) ori r4,r1,80

assign rom[5'h02] = 32'h20050004; // (08) addi r5,r0, 4

assign rom[5'h03] = 32'h0c000018; // (0c)call: jal sum

assign rom[5'h04] = 32'hac820000; // (10) sw r2,0(r4)

assign rom[5'h05] = 32'h8c890000; // (14) lw r9, 0(r4)

assign rom[5'h06] = 32'h01244022; // (18) sub r8, r9. r4

assign rom[5'h07] = 32'h20050003; // (lc) addi r5, r0. 3

assign rom[5'h08] = 32'h20a5ffff; // (20) loop2: addi r5, r5, -1

assign rom[5'h09] = 32'h34a8ffff; // (24) ori r8, r5, 0xffff

assign rom[5'h0A] = 32'h39085555; // (28) xori r8. r8, 0x5555

assign rom[5'h0B] = 32'h2009ffff; // (2c) addi r9, rO, -1

assign rom[5'h0C] = 32'h312affff; // (30) andi rlO, r9, 0xffff

assign rom[5'h0D] = 32'h01493025; // (34) or r6. rlO, r9

assign rom[5'h0E] = 32'h01494026; // (38) xor r8, rlO, r9

assign rom[5'h0F] = 32'h01463824; // (3c) and r7, rlO, r6

assign rom[5'h10] = 32'h10a00001; // (40) beq r5, r0, shift

assign rom[5'h11] = 32'h08000008; // (44) j loop2

assign rom[5'h12] = 32'h2005ffff; // (48) shift: addi r5. r0, -1

assign rom[5'h13] = 32'h000543c0; // (4c) sll r8. r5. 15

assign rom[5'h14] = 32'h00084400; // (50) sll r8, r8, 16

assign rom[5'h15] = 32'h00084403; // (54) sra r8, r8, 16

assign rom[5'h16] = 32'h000843c2; // (58) srl r8. r8. 15

assign rom[5'h17] = 32'h08000017; // (5c) finish: j finish

assign rom[5'h18] = 32'h00004020; // (60) sum: add r8, r0, r0

assign rom[5'h19] = 32'h8c890000; // (64) loop: lw r9, (r4)

assign rom[5'h1A] = 32'h20840004; // (68) addi r4, r4, 4

assign rom[5'h1B] = 32'h01094020; // (6c) add r8, r8, r9

assign rom[5'h1C] = 32'h20a5ffff; // (70) addi r5, r5, -1

assign rom[5'h1D] = 32'h14a0fffb; // (74) bne rS, r0, loop

assign rom[5'h1E] = 32'h00081000; // (78) sll r2f r8f 0

assign rom[5'h1F] = 32'h03e00008; // (7c) jr r31

// 將地址對應的資料放入inst

assign inst = rom[a[6:2]];

endmodulescdatamem.v

/*將資料寫入RAM中(隨機存取儲存器)的指定位置*/

/*輸入待寫資料datain、目標地址addr;寫使能訊號we;時鐘訊號clk、inclk、outclk*/

/*輸出將被覆蓋的資料dataout*/

module scdatamem (clk,dataout,datain,addr,we,inclk,outclk);

input [31:0] datain;

input [31:0] addr ;

input clk, we, inclk, outclk;

output [31:0] dataout;

reg [31:0] ram [0:31]; // 定義32個32位RAM

// 把將被覆蓋的資料放入dataout

assign dataout =ram[addr[6:2]];

// 時序邏輯,clk的上升沿觸發

always @ (posedge clk) begin

if (we) ram[addr[6:2]] = datain; // 如果寫使能訊號we為1,將資料寫入目標地址

end

// 為RAM賦值,這一步不是必要的,只是欲執行的自定義程式的需要。

integer i;

initial begin

for (i = 0;i < 32;i = i + 1)

ram[i] = 0;

ram[5'h14] = 32'h000000a3;

ram[5'h15] = 32'h00000027;

ram[5'h16] = 32'h00000079;

ram[5'h17] = 32'h00000115;

end

endmodulesccu_dataflow.v

/*基於MIPS指令集的控制器*/

/*輸入指令的op欄位、func欄位、z訊號*/

/*輸出wreg,regrt,aluc,pcsource等等控制訊號*/

module sccu_dataflow (op,func,z,wmem,wreg,regrt,m2reg,aluc,shift,aluimm,pcsource,jal,sext);

input [5:0] op,func;

input z;

output wreg,regrt,jal,m2reg,shift,aluimm,sext,wmem;

output [3:0] aluc;

output [1:0] pcsource;

// 確定內部訊號r_type的值

wire r_type = ~|op;

// 如果r_type為真,根據func,確定是哪一種R型指令

wire i_add = r_type&func[5]&~func[4]&~func[3]&~func[2]&~func[1]&~func[0];

wire i_sub = r_type&func[5]&~func[4]&~func[3]&~func[2]&func[1]&~func[0];

wire i_and = r_type&func[5]&~func[4]&~func[3]&func[2]&~func[1]&~func[0];

wire i_or = r_type&func[5]&~func[4]&~func[3]&func[2]&~func[1]&func[0];

wire i_xor = r_type&func[5]&~func[4]&~func[3]&func[2]&func[1]&~func[0];

wire i_sll = r_type&~func[5]&~func[4]&~func[3]&~func[2]&~func[1]&~func[0];

wire i_srl = r_type&~func[5]&~func[4]&~func[3]&~func[2]&func[1]&~func[0];

wire i_sra = r_type&~func[5]&~func[4]&~func[3]&~func[2]&func[1]&func[0];

wire i_jr = r_type&~func[5]&~func[4]&func[3]&~func[2]&~func[1]&~func[0];

// 如果r_type為假,根據op,確定是哪一種指令

wire i_addi = ~op[5]&~op[4]&op[3]&~op[2]&~op[1]&~op[0];

wire i_andi = ~op[5]&~op[4]&op[3]&op[2]&~op[1]&~op[0];

wire i_ori = ~op[5]&~op[4]&op[3]&op[2]&~op[1]&op[0];

wire i_xori = ~op[5]&~op[4]&op[3]&op[2]&op[1]&~op[0];

wire i_lw = op[5]&~op[4]&~op[3]&~op[2]&op[1]&op[0];

wire i_sw = op[5]&~op[4]&op[3]&~op[2]&op[1]&op[0];

wire i_beq = ~op[5]&~op[4]&~op[3]&op[2]&~op[1]&~op[0];

wire i_bne = ~op[5]&~op[4]&~op[3]&op[2]&~op[1]&op[0];

wire i_lui = ~op[5]&~op[4]&op[3]&op[2]&op[1]&op[0];

wire i_j = ~op[5]&~op[4]&~op[3]&~op[2]&op[1]&~op[0];

wire i_jal = ~op[5]&~op[4]&~op[3]&~op[2]&op[1]&op[0];

// 在確定了指令的情況下,確定控制訊號的取值

assign wreg = i_add|i_sub|i_and|i_or|i_xor|i_sll|i_srl|i_sra|i_addi|i_andi|i_ori|i_xori|i_lw|i_lui|i_jal;

assign regrt= i_addi|i_andi|i_ori|i_xori|i_lw|i_lui;

assign jal= i_jal;

assign m2reg= i_lw;

assign shift=i_sll|i_srl|i_sra;

assign aluimm=i_addi|i_andi|i_ori|i_xori|i_lw|i_lui|i_sw;

assign sext =i_addi|i_lw|i_sw|i_beq|i_bne;

assign aluc[3]=i_sra;

assign aluc[2]=i_sub|i_or|i_srl|i_sra|i_ori|i_lui;

assign aluc[1]=i_xor|i_sll|i_sra|i_xori|i_beq|i_bne|i_lui;

assign aluc[0]=i_and|i_or|i_sll|i_srl|i_sra|i_andi|i_ori;

assign wmem = i_sw;

assign pcsource[1]=i_jr|i_j|i_jal;

assign pcsource[0]=i_beq&z|i_bne&~z|i_j|i_jal;

endmodulemux2x32.v

/*32位二路選擇器*/

/*輸入決定選擇哪一路的控制訊號s,輸入待選擇的訊號a0、a1*/

/*輸出被選擇的訊號y*/

module mux2x32 (a0,a1,s,y);

input [31:0] a0,a1;

input s;

output [31:0] y;

assign y = s?a1:a0; // 如果s為1,選擇a1,否則選擇a0

endmodulemux2x5.v

/*5位二路選擇器*/

/*邏輯同上*/

module mux2x5 (a0,a1,s,y);

input [4:0] a0,a1;

input s;

output [4:0] y;

assign y = s?a1:a0;

endmodulemux4x32.v

/*32位四路選擇器*/

/*待選擇的數是a0~a3,控制訊號為s,選擇結果為y*/

/*s如何控制,由case語句決定*/

module mux4x32 (a0,a1,a2,a3,s,y);

input [31:0] a0,a1,a2,a3;

input [1:0] s;

output [31:0] y;

function [31:0] select;

input [31:0] a0,a1,a2,a3;

input [1:0] s;

case (s)

2'b00: select = a0; //s為00時,選擇a0

2'b01: select = a1;

2'b10: select = a2;

2'b11: select = a3;

endcase

endfunction

assign y = select(a0,a1,a2,a3,s); // y為選擇的結果

endmoduledff32.v

/*將資料送入指定暫存器*/

/*輸入待存資料d,待存暫存器q;時鐘clk和clrn*/

/*沒有輸出*/

module dff32(d,clk,clrn,q);

input [31:0] d;

input clk,clrn;

output [31:0] q;

reg [31:0] q;

/*時序邏輯,clk的上升沿降沿觸發、clrn的下降沿觸發*/

always @ (negedge clrn or posedge clk)

// clrn是清零時鐘

if (clrn == 0) begin // 當清零時鐘到來時

q <= 0; // 為q賦值0

end else begin

q <= d; // 否則賦值d

end

endmodulecla32.v

/*下面所有程式都是為了實現一個東東:32位並行加法器*/

/*從最基本的加法進位模型add實現全加器cla_2,

逐步整合為4位全加器cla_4、8位的全加器cla_8、

16位全加器cla_16、32位全加器cla_32,

最終實現32位並行加法器cla32

*/

/*加數是a、b,和是s*/

/*借位是ci,進位是co*/

module cla32 (a,b,ci,s,co);

input [31:0] a,b;

input ci;

output [31:0] s;

output co;

wire g_out, p_out;

cla_32 cla (a,b, ci,g_out,p_out, s); // 向下呼叫

assign co = g_out| p_out & ci;

endmodule

module add(a,b,c,g,p,s);

input a,b,c;

output g,p,s;

assign s = a^b^c;

assign g = a & b;

assign p = a | b;

endmodule

module g_p (g,p,c_in,g_out,p_out,c_out);

input [1:0] g,p;

input c_in;

output g_out, p_out, c_out;

assign g_out = g[1]|p[1] & g[0];

assign p_out = p[1] & p[0];

assign c_out = g[0] | p[0] & c_in;

endmodule

module cla_2 (a,b,c_in,g_out,p_out,s) ;

input [1:0] a,b;

input c_in;

output g_out, p_out;

output [1:0] s;

wire [1:0] g,p;

wire c_out;

add add0 (a[0],b[0],c_in, g[0],p[0],s[0]);

add add1 (a[1],b[1],c_out, g[1],p[1],s[1]);

g_p g_p0 (g,p,c_in, g_out,p_out,c_out);

endmodule

module cla_4 (a,b, c_in,g_out,p_out,s);

input [3:0] a,b;

input c_in;

output g_out, p_out;

output [3:0] s;

wire [1:0] g,p;

wire c_out;

cla_2 cla0 (a[1:0],b[1:0],c_in, g[0],p[0],s[1:0]);

cla_2 clal (a[3:2],b[3:2],c_out,g[1],p[1],s[3:2]);

g_p g_p0 (g,p,c_in, g_out,p_out,c_out);

endmodule

module cla_8 (a,b, c_in,g_out,p_out, s);

input [7:0] a,b;

input c_in;

output g_out, p_out;

output [7:0] s;

wire [1:0] g,p;

wire c_out;

cla_4 cla0 (a[3:0],b[3:0],c_in, g[0],p[0],s[3:0]);

cla_4 c1a1 (a[7:4],b[7:4],c_out,g[1],p[1],s[7:4]);

g_p g_p0 (g,p,c_in, g_out,p_out,c_out);

endmodule

module cla_16 (a,b, c_in,g_out,p_out, s);

input [15:0] a,b;

input c_in;

output g_out, p_out;

output [15:0] s;

wire [1:0] g,p;

wire c_out;

cla_8 cla0 (a[7:0],b[7:0],c_in,g[0],p[0],s[7:0]);

cla_8 cla1 (a[15:8],b[15:8],c_out,g[1],p[1],s[15:8]);

g_p g_p0 (g,p,c_in, g_out,p_out,c_out);

endmodule

module cla_32 (a,b,c_in,g_out,p_out, s);

input [31:0] a,b;

input c_in;

output g_out, p_out;

output [31:0] s;

wire [1:0] g,p;

wire c_out;

cla_16 c1a0 (a[15:0],b[15:0],c_in,g[0],p[0],s[15:0]);

cla_16 c1a1 (a[31:16],b[31:16],c_out,g[1],p[1],s[31:16]);

g_p g_p0 (g,p,c_in, g_out,p_out,c_out);

endmoduleaddsub32.v

/*32位加減運算模組*/

/*呼叫32位加法模組*/

/*是加是減,取決於sub的取值*/

module addsub32(a,b,sub,s);

input [31:0] a,b;

input sub;

output [31:0] s;

cla32 as32 (a,b^{32{sub}},sub,s);

endmodulealu.v

/*alu算數邏輯單元*/

/*輸入運算元a、b,操作型別訊號aluc*/

/*輸出運算結果r;z是?*/

module alu (a,b,aluc,r,z);

input [31:0] a,b;

// aluc是3位的,每一位都有作用,見下

input [3:0] aluc;

output [31:0] r;

output z;

wire [31:0] d_and = a & b; // 求和

wire [31:0] d_or = a | b; // 求或

wire [31:0] d_xor = a ^ b; // 求異或

wire [31:0] d_lui = {b[15:0],16'h0}; // 拼接,低16位補0

wire [31:0] d_and_or = aluc[2]? d_or : d_and; // aluc[2]決定 與/或

wire [31:0] d_xor_1ui= aluc[2]? d_lui : d_xor; // aluc[2]決定 異或/拼接

wire [31:0] d_as,d_sh; // 加減法結果儲存到d_as中;移位結果存入d_sh中

// aluc[2]控制加減法

addsub32 as32 (a,b,aluc[2],d_as);

// b為待移的數,a[4:0]為移動位數,aluc[2]決定左右移,aluc[3]決定補全方式,結果儲存在d_sh中

shift shifter (b,a[4:0],aluc[2],aluc[3],d_sh) ;

// 四路選擇,aluc[1:0]控制選擇哪一路,r為選擇結果

mux4x32 se1ect (d_as,d_and_or, d_xor_1ui, d_sh, aluc[1:0],r);

assign z = ~|r;

endmodule regfile.v

/*讀暫存器堆、寫暫存器堆*/

/*輸入將要讀取哪一個暫存器rna、rnb;輸出讀出的內容qa、qb*/

/*輸入寫使能we、待寫入的暫存器wn,待寫入的資料d*/

/*輸入時鐘clk、clrn*/

module regfile (rna, rnb, d, wn,we, clk, clrn, qa, qb);

input [4:0] rna,rnb,wn;

input [31:0] d;

input we, clk, clrn;

output [31:0] qa,qb;

reg [31:0] register [1:31]; // 定義32個32位暫存器

// 讀暫存器

// 如果指定的是rna,即rna不為0,將rna暫存器中的內容放入qa

assign qa = (rna == 0) ? 0 : register[rna];

// 如果指定的是rnb,即rnb不為0,將rnb暫存器中的內容放入qb

assign qb = (rnb == 0) ? 0 : register[rnb];

// 寫暫存器

// 時序邏輯,clk的上升沿或clrn的下降沿觸發

always @(posedge clk or negedge clrn)

begin

if (clrn==0) // 當為清空時鐘訊號時

begin

integer i;

for(i=1;i<32;i=i+1)

register[i] <= 0; // 清空所有暫存器

end

else if((wn!=0)&&we) // 當寫使能為邏輯1,且wn不是0時

register[wn] <= d; // 將d寫入wn暫存器

end

endmodulesccpu_dataflow.v

/*cpu*/

/*輸入時鐘訊號clock、是否進行清零的訊號resetn*/

/*輸入32位指令inst、以及其他值*/

module sccpu_dataflow(clock, resetn, inst, mem, pc, wmem, alu, data);

input [31:0] inst,mem;

input clock, resetn;

output [31:0] pc,alu,data;

output wmem;

wire [31:0] p4 , bpc, npc, adr, ra, alua, alub, res, alu_mem;

wire [3:0] aluc;

wire [4:0] reg_dest, wn;

wire [1:0] pcsource;

wire zero, wmem, wreg, regrt, m2reg, shift, aluimm, jal, sext;

wire [31:0] sa = {27'b0,inst[10:6]};

wire [31:0] offset = {imm[13:0],inst[15:0],2'b00};

/*控制器*/

// 輸入inst[31:26]即op欄位、inst[5:0]即func欄位、0標誌位zero

// 輸出wmem、wreg等控制訊號

sccu_dataflow cu (inst[31:26] , inst[5:0] , zero, wmem,wreg,regrt,m2reg, aluc, shift, aluimm,pcsource, jal, sext);

/*0拓展或符號拓展*/

wire e = sext & inst[15]; // 取出0或者符號

wire [15:0] imm = {16{e}};

wire [31:0] immediate = {imm,inst[15:0]}; // 拼接、拓展

/*修改PC,使PC指向下一條地址*、

dff32 ip (npc,clock,resetn,pc); // 將npc(即下一條指令的地址)寫入暫存器pc

/*計算下地址*/

// 四路選擇器的0路

cla32 pcplus4 (pc,32'h4,1'b0,p4); // pc和32位十六進位制4相加,再加上進位0,結果放入p4

// 四路選擇器的1路

cla32 br_adr (p4,offset,1'b0, adr); // p4和拓展後的imm相加,再加上進位0,結果放入adr

// 四路選擇器的3路

wire [31:0] jpc = {p4[31:28],inst[25:0],2'b00}; // 如圖

/*二路選擇器*/

// ③號。在ra即q1、sa之間選擇,控制訊號是shift,選擇結果為alua

mux2x32 alu_a (ra,sa,shift,alua);

// ④號。在data即q2、immediate之間選擇,控制訊號是aluimm,選擇結果為alub

mux2x32 alu_b (data, immediate,aluimm, alub);

// ⑤號。在alu即r、mem即do之間選擇,控制訊號是m2reg,選擇結果為alu_mem

mux2x32 result (alu,mem,m2reg,alu_mem);

// ②號。在alu_mem、p4之間選擇,控制訊號是jal即call,選擇結構是res

mux2x32 link (alu_mem,p4,jal,res);

// ①號。在inst[15:11]即rd,inst[20: 16]即rt之間選擇,控制訊號是regrt,選擇結果是reg_dest

mux2x5 reg_wn (inst[15:11], inst[20: 16] , regrt, reg_dest);

// 對應圖中的①號後面的f器件(不知道做什麼的...)

assign wn = reg_dest | {5{jal}};

/*四路選擇器,計算下地址*/

// 在p4、adr即addr、ra即q1、jpc即p4+immidiate<<2,之間選擇,控制訊號是pcsource,選擇結果是npc

mux4x32 nextpc (p4,adr,ra, jpc,pcsource,npc);

/*暫存器組*/

// 定義一個暫存器,輸入埠是inst[25:21]即rs(n1)、inst[20:16]即rt(n2)

// 輸出埠是data即ra即q1、data即q2

// 輸入寫使能wreg、待寫暫存器wn即n

// 輸入時鐘clock即clk、清零時鐘resetn

regfile rf (inst[25:21] ,inst[20:16] ,res,wn,wreg,clock,resetn,ra,data);

/*alu*/

// 運算元是alua、alub,操作結果是aluu空r、標誌位zero即z

// 控制訊號是aluc

alu al_unit (alua,alub,aluc,alu, zero);

endmodulesccmop_dataflow.v

/*最頂層的控制模組*/

/*輸入時鐘clock和resetn*/

/*輸出 指令inst、PC的值pc、ALU的運算結果aluout、儲存器的輸出memout、時鐘訊號mem_clk*/

module sccomp_dataflow(clock, resetn, inst, pc, aluout, memout,mem_clk);

input clock, resetn,mem_clk;

output [31:0] inst,pc, aluout,memout;

wire [31:0] data;

wire wmem;

// 例項化一個cpu

sccpu_dataflow s (clock, resetn, inst,memout,pc, wmem, aluout, data);

// 例項化一個ROM

scinstmem imem (pc,inst);

// 例項化一個RAM

scdatamem dmem (clock, memout, data, aluout, wmem, mem_clk, mem_clk);

endmodule