【併發程式設計】摩爾定律失效“帶來”並行程式設計

併發和並行

在真正開始聊本文的主題之前,我們先來回顧下兩個老生常談的概念:併發和並行。

- 併發:是指多個執行緒任務在同一個CPU上快速地輪換執行,由於切換的速度非常快,給人的感覺就是這些執行緒任務是在同時進行的,但其實併發只是一種邏輯上的同時進行;

- 並行:是指多個執行緒任務在不同CPU上同時進行,是真正意義上的同時執行。

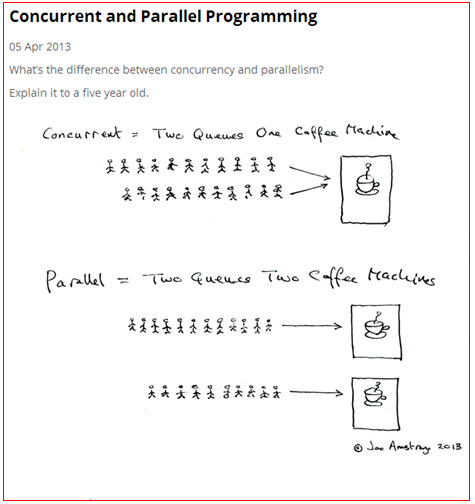

下面貼上一張圖來解釋下這兩個概念:

上圖中的咖啡就可以看成是CPU,上面的只有一個咖啡機,相當於只有一個CPU。想喝咖啡的人只有等前面的人制作完咖啡才能製作自己的開發,也就是同一時間只能有一個人在製作咖啡,這是一種併發模式。下面的圖中有兩個咖啡機,相當於有兩個CPU,同一時刻可以有兩個人同時製作咖啡,是一種並行模式。

我們發現並行程式設計中,很重要的一個特點是系統具有多核CPU。要是系統是單核的,也就談不上什麼並行程式設計了。那麼是什麼原因導致了現代CPU架構都是多核架構?如果CPU架構都是單核的架構我們是不是就能不要研究什麼並行程式設計了?

"摩爾定律"失效

上面章節中留下了一個問題:為什麼現代CPU都是多核架構。為了回答這個問題,我們先來了解一個定律--摩爾定律。

1965年,英特爾聯合創始人戈登·摩爾提出以自己名字命名的「摩爾定律」,意指積體電路上可容納的元器件的數量每隔 18 至 24 個月就會增加一倍,效能也將提升一倍。

根據摩爾定律,CPU的效能每隔18到24個月就能增長一倍。但是從現在的情況來看,單核CPU的主頻已經逼近了極限,以現在的製造工藝,很難再繼續提升單核CPU的主頻。也就是說摩爾定律已經失效。

雖然摩爾定律失效了,但是科技的進度對CPU效能的需求沒有停止。這個也難不倒我們偉大的硬體工程師。一個CPU的效能提升有限,我將兩個CPU拼在一起效能不就提升一倍了麼。於是多核CPU的架構就出現了。

提高CPU工作主頻主要受到生產工藝的限制。由於CPU是在半導體矽片上製造的,在矽片上的元件之間需要導線進行聯接,由於在高頻狀態下要求導線越細越短越好,這樣才能減小導線分佈電容等雜散干擾以保證CPU運算正確。因此製造工藝的限制,是CPU主頻發展的最大障礙之一。

多核架構引發並行程式設計

為了繼續保持效能的高速發展,硬體工程師破天荒地想出了將多個CPU核心塞進一個CPU裡的奇妙想法。由此,平行計算就被非常自然地推廣開來,隨之而來的問題也層出不窮,程式設計師的黑暗時期也隨之到來。簡化的硬體設計方案必然帶來軟體設計的複雜性。換句話說,軟體工程師正在為硬體工程師無法完成的工作負責,他們將摩爾定律失效的責任推給了軟體開發者。

所以,如何讓多個CPU有效並且正確地工作也就成了一門技術,甚至是很大的學問。比如,多執行緒間如何保證執行緒安全,如何正確理解執行緒間的無序性、可見性,如何儘可能地設計並行程式,如何將序列程式改造為並行程式。而對平行計算的研究,也就是希望給這片黑暗帶來光明。

總結

世界就是這樣一個矛盾體,併發程式設計能讓我們充分地利用CPU資源,提升系統性能。但是同時也給我們帶來了很多問題,比如執行緒上下文切換對效能消耗的問題、共享變數的執行緒安全問題、執行緒死鎖問題和執行緒間通訊等問題。研究並行程式設計就是研究怎麼在享受多執行緒程式設計給我們帶來便利的同時又能規避多執行緒帶來的坑。