FPGA實現DDS方案

一、DDS的系統結構

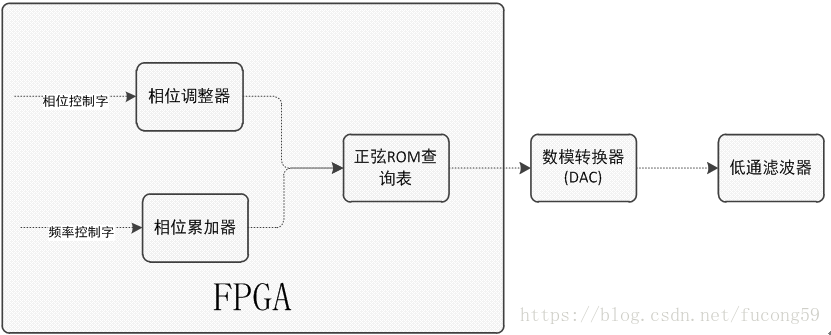

DDS是直接數字式頻率合成器(Direct Digital Synthesizer),系統結構可分為如下幾個部分,其中相位控制字可調整輸出正弦波的相位,頻率控制字可以調整輸出正弦波的頻率。DAC把FPGA輸出的數字量轉換成模擬訊號,因為訊號中有大量高頻訊號,再加一級的低通濾波器可以使訊號變得更加平滑。

圖1:系統框圖

二、實現基本原理

通過MATLAB可以生成一組2^N個點的正弦波查詢表,如果系統時鐘(Fclk)按地址加1的順序迴圈讀取ROM查詢表的值,則可以產生一個週期為fclk/2^N的一個正弦波訊號(稱為基頻)。因為系統時鐘不能改變,而如果想得到更高頻率的訊號,可以通過減少輸出ROM查詢表的點的方法(跳過ROM表中的一些值)來加快ROM表週期讀取實現,而如果想得到更低的頻率,則可以通過重複輸出一個點的值來減慢ROM表週期的讀取來實現。

三、系統引數選擇

相位累加器是實現DDS的核心,ROM的位寬和深度、系統時鐘頻率、相位累加器的寬度的引數選擇是設計滿足要求需要考慮的重要引數,這裡通過一個例子說明:

假設系統時鐘為50M, ROM的位寬為8位,即把一個正弦波的峰峰值用8位資料(256個點)來量化,則需要512個點去表示一個週期的正弦波,設定ROM表的深度為512。

因為ROM的深度為512(2^9)位,所以相位累加器要大於9位,只需取高9位作為ROM的輸入地址,低位作為累計量。假設相位累加器是16位位寬,因此高9位作為ROM的地址輸入。

頻率控制字是相位累計器每次加的值,如果我們要得到這個假設系統的基頻,則需要每個時鐘沿都對ROM的地址加1,即16位相位累加器的第7位加1(見圖2),則輸入的控制字Fword為1000_0000,產生的基頻為50M/512= 97656.25Hz,其中512是ROM的深度,也是2^16迴圈計數一次的個數,其取值為2^16/Fword。所以輸出頻率(Fout)可以用公式表示為:Fout=50M/(2^16/Fword)。假設系統頻率為Fclk,相位累加器的位寬為N,則Fout=(Fclk*Fword)/2^N。我們可以通過設定不同的Fword大小來調節輸出的正弦波頻率。

圖2:每次對第7位加1

在這個例子中Fword每加1即輸出頻率改變50M/2^16= 762.939453125,所以輸出頻率的最小解析度約為763Hz,系統輸出的最小頻率也為763Hz;又因為當不斷增加輸出正弦波的頻率的時候會跳過很多點去取樣ROM表的資料,對於本例中如果系統要求一個週期必須輸出16個正弦波的取樣點,則滿足要求的最大正弦波頻率為50M/16=3.125MHz,則該設計滿足要求的頻率約為763Hz~3.125MHz,其中輸出正弦波頻率的最小解析度約為763Hz。

由此可以知道在設計一個優良DDS之前首先我們需要知道DAC的位寬、輸出頻率範圍、頻率解析度和最小週期取樣點個數,根據這些要求我們可以通過計算出滿足要求的系統的時鐘頻率、ROM位寬,資料深度、相位累加器的寬度這些引數滿足設計的需求。

相位調整器是在把每次給ROM表的地址加上一個輸入的一個固定偏移量即相位控制字Fphase,其位寬和ROM的地址位寬相同即可。

四、設計一個輸出3KHz-3MHz的正弦波

假設要求輸出每個正弦波的週期點為64個,因為最大的輸出頻率為3M,所以系統時鐘至少應該為64*3M=192M。

假設DAC的位寬為16位,則為了儘可能利用好DAC的精度,我們設計ROM的位寬為16位,資料深度為131072。假設DAC的最大輸出電壓為5V則量化精度可以達到5V/65536≈0.0763mV。

因為輸出頻率的最小值為3k,累加器的寬度為log(192M/3k)≈15.965784,所以至少累加器需要設定為16位位寬。為了能達到更好的頻率解析度,我們設計累加器的計數位寬為32位,則該系統的輸出頻率解析度為192M/(2^32)≈0.0447Hz。