80386指令流水線及其優化

80386 Architecture Overview

80386是Intel的第一代32位x86架構處理器,內部32位的資料通路,外部32位的資料匯流排與地址匯流排,標誌著32位程式設計時代的到來。硬體層面上的特權級指令,多工,32位保護模式,虛擬記憶體管理等機制為32位的多使用者多工作業系統提供了原生支援,具有劃時代的意義。

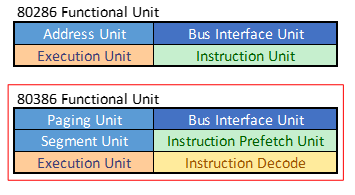

80386架構主要有以下主要的單元構成:匯流排介面單元,指令預取單元,指令譯碼單元,記憶體管理單元(包括段管理單元和分管理單元),以及執行單元。相比起80286,386新增了獨立指令譯碼單元。286的地址單元擴張成了記憶體管理單元,由獨立的段管理單元和頁管理單元構成,所以有時也稱386的記憶體管理是段頁式管理機制。

下圖是一個較為詳細的Intel386™ DX處理器的功能模組圖。對該圖的詳細講解會放在其他章節裡,這裡供讀者參考。

80386 Instruction Pipeline Details

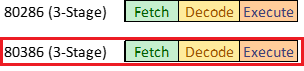

80386依然使用了類似於286的3級流水線:取指,譯碼和執行。

需要注意的是,從下圖中可以看出在某些情況下,下一條指令的地址計算可以和當前指令的執行並行進行,在某種程度上增加了並行度,提升了指令的吞吐量。但是地址計算並不是80386指令流水線中獨立的一級。

Instruction Prefetcher

指令預取單元從外部儲存器中讀取指令流。預取到的指令臨時儲存在4-deep,4-byte-wide的預取快取中(TODO: 是不是意味著指令快取是4x4=16位元組?)。這些指令接下來將會由指令譯碼器處理。

注:由於x86指令屬於變長指令格式,預取快取中的指令並沒有劃分出指令邊界,所以我們稱之為指令流。

Instruction decoder

指令譯碼器將譯碼後的指令儲存在一個3-deep(TODO: 意味著可以儲存3條已譯碼的指令)的先入先出佇列中,這個佇列被稱為已譯碼指令佇列。指令譯碼器將指令預取單元和處理器執行核解耦合,與兩者都有各自的通訊協議。

Execution Core

處理器執行核(即前兩代產品中執行單元EU)一次執行一條指令。在某些條件下,當前指令的最後一個時鐘週期可以與下一條指令的有效地址計算重疊在一起執行,參看下圖中的MMU部分(以紅線標出)。

Optimization Consideration

從編譯器開發人員的角度來看,指令預取/譯碼/執行3階段 的解耦合, 執行核的順序執行特徵,這兩點幾乎都沒有對指令的排程提出太多需求。在計算有效地址時避免使用索引暫存器可以節省一個時鐘週期。 最好的優化方法就是非常小心的選擇指令使得執行時間最小化。