FPGA入門筆記一 RTL級設計與晶片的關聯

第一次寫部落格,同時也表示學習FPGA的決心。

學習的初步目標是能夠駕馭XILINX XC7K325T,寫點簡單的程式,或者用起來別人的複雜程式碼。預期一個月。

從簡單入手可能更容易理解,使用黑金開發板AX309,型號SPARTAN-6 XC6SLX9。

跑了幾個程式之後,發現別人的程式越來越不好理解,在沒有備註的情況下更難,於是想搞清楚寫程式的邏輯是什麼。看了很多關於說編寫verilog與編寫C語言思想完全不同的文章,verilog是一種硬體描述語言要時刻想到底層的電路,但是1、這個底層電路到底指的什麼呢?2、與verilog之間的關係是什麼呢?

RTL級,register transfer level,指的是用暫存器這一級別的描述方式來描述電路的資料流方式;而Behavior級指的是僅僅描述電路的功能而可以採用任何verilog語法的描述方式。鑑於這個區別,RTL級描述的目標就是可綜合,而行為級描述的目標就是實現特定的功能而沒有可綜合的限制。當然,RTL級描述也是採用的verilog,但是是verilog中的可綜合子集。既然描述物件是暫存器,就要了解FPGA的基本組成了。

register transfer level

FPGA晶片主要由三部分組成,分別是IOE(input output element,輸入輸出單元)、LAB(logic array block,邏輯陣列塊,對於Xilinx稱之為可配置邏輯塊CLB)和Interconnect(內部連線線)。

CLB包含了LUT(Look-Up-Table查詢表)、觸發器、相關邏輯。LUT(Look-Up-Table)其本質是一個靜態儲存器SRAM,目前FPGA多采用4輸入的LUT,每個LUT可以看作一個有4位地址線的16x1的RAM。當我們通過原理圖或HDL語言描述了一個邏輯電路後,FPGA開發軟體會自動計算邏輯電路的所有可能的結果,並把結果事先寫入RAM。這樣,在FPGA工作時,每輸入一個訊號進行邏輯運算就等於輸入一個地址進行查表,找出地址對應的內容,然後輸出。

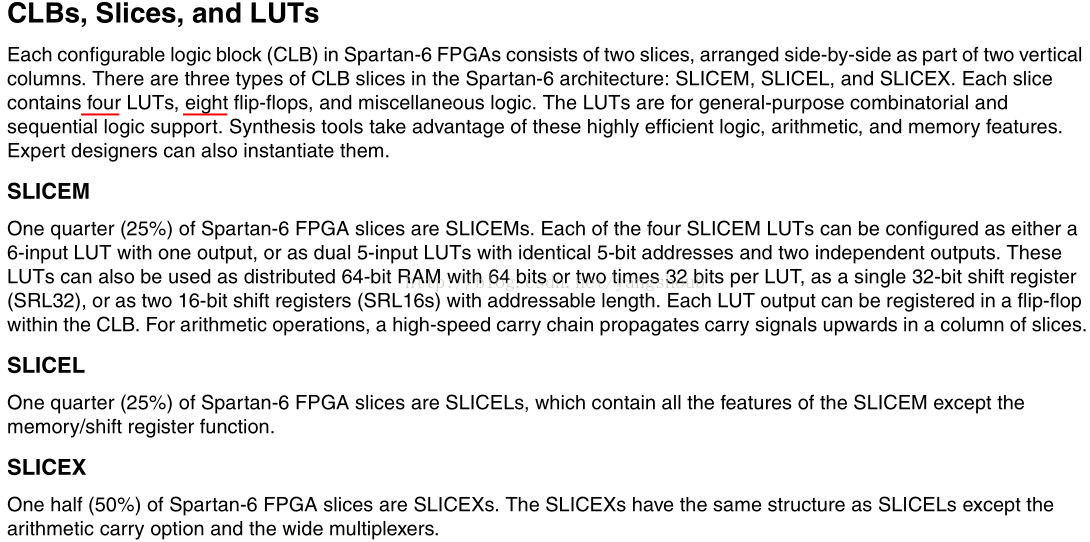

不同型號晶片中的CLB不同,就要看Dadasheet了,下述是SPARTAN-6的。

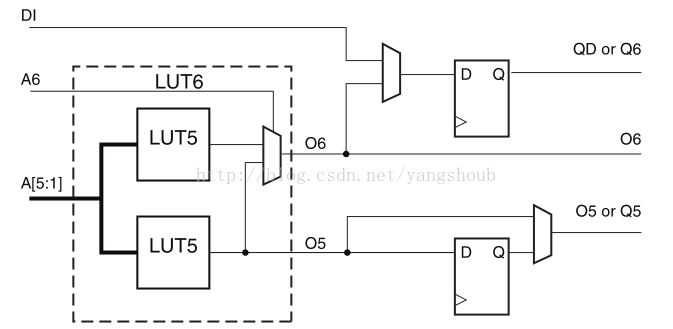

LUT的結構圖示意如下:

這些晶片屬性的基礎資訊要了然於心,程式設計過程中要有所體味。到此也回答了文章開始的第一個問題。

Verilog程式設計(可綜合子集,RTL級)的程式碼如何與電路建立聯絡就得從語言本身說起了,所謂硬體描述語言:就是指雖然是語言,但是形容的內容是硬體。比如reg相當於儲存單元,wire相當於物理連線,and與門,or或門,bufif/notif帶控制端的緩衝器/非門;每一個always語句或者assign語句都代表一條獨立的電路,而這些電路都是[email protected]

這樣應該可以理解第二個問題了,但是貌似還少了些什麼,就是根據什麼程式設計呢?那就是功能設計。

一般都採用自頂向下的設計方法,把系統分成若干個基本單元,然後再把每個基本單元劃分為下一層次的基本單元,一直這樣做下去,直到可以直接使用門或者連線線為止。要根據演算法或者硬體的工作原理,內在邏輯認真分析行為模型,確定需要的暫存器型別和數量,再確定執行時序,狀態機等,然後就是程式設計了。

具體RTL 設計步驟: 功能定義與模組劃分;定義所有模組的介面; 設計時鐘域; 考慮設計的關鍵路徑; 頂層設計; FSM 設計; 時序邏輯設計; 組合邏輯設計。

常用的RTL建模: 阻塞賦值、非阻塞賦值和連續賦值; 暫存器電路建模; 組合邏輯建模; 雙向埠與三態訊號建模; Mux建模; 儲存器建模; 簡單的時鐘分頻電路; 串並轉換建模; 同步復位與非同步復位; case語句和if語句建模; 可綜合的Verilog語法子集

引用:

1、FPGA組成、工作原理和開發流程 http://blog.csdn.net/loongembedded/article/details/7182900

2、RTL級設計 https://wenku.baidu.com/view/49e3e33a87c24028915fc363.html

3、DATASheet :Spartan-6 Family Overview 中文版 https://wenku.baidu.com/view/60d73684ec3a87c24028c4d9.html

4、DATASheet :Spartan-6 FPGA Configurable Logic Block User Guide 中文 https://wenku.baidu.com/view/e400a4576137ee06eff918a5.html