轉發:Xilinx 7series FPGA SelectIO資源--ODDR

OLOGIC 資源

OLOGIC塊在FPGA內的位置緊挨著IOB,其作用是FPGA通過IOB傳送資料到器件外部的專用同步塊。OLOGIC 資源的型別有OLOGIC2(位於HP I/O banks)和OLOGIC2(位於HR I/O banks)。在本文的下述論述中,除非特殊說明,OLOGIC2和OLOGIC3在功能和埠上都是相同的。

OLOGIC2和OLOGIC3不屬於原語,正因為這樣,所以它們不能被直接例化。它包含在佈局佈線後用戶可例化的一些元素,例如一個輸出觸發器(OFD--output flip-flop)或者一個ODDR(output DDR element).

OLOGIC主要由兩個block組成,一個用於配置輸出路徑。另外一個用於配置三態控制路徑。這兩個block具有共同的時鐘,但是具有不同的使能訊號OCE和TCE。兩者具有由SRVAL屬性精緻的一部和同步set和reset(S/R訊號)。

輸出路徑和三態枯井可以以下列模式之一獨立配置:

- 邊沿觸發的D觸發器

- DDR模式(ASAME_EDGE 或 OPPOSITE_EDGE)

- 電平敏感鎖存器

- 非同步電路/組合邏輯

組合輸出資料路徑和三態控制路徑

組合輸出路徑建立一個從FPGA邏輯到輸出驅動或輸出驅動控制的直接連線。這些路徑常常由軟體自動設定,當:

- 從FPGA邏輯內的邏輯資源到輸出資料或者三態控制的直接連線(未經過暫存器)。

- pack i/o register/larches into IOBs 軟體map指令被設定為OFF。

Output DDR概述(ODDR)

7系列器件在OLOGIC中有專用暫存器來實現輸出DDR暫存器。這個功能在例化ODDR時可見。在使用OLOGIC時,DDR的複用是自動的,不需要手動控制多路複用。這個控制是從時鐘產生的。

ODDR原語是由一個時鐘輸入,下降沿資料由輸入時鐘的本地反轉來計時。反饋到I/O塊的所有的時鐘被完全複用。例如:在ILOGIC和OLOGIC塊之間沒有時鐘共享。ODDR原語支援一下操作模式:

- OPPOSITE_EDGE 模式

- SAME_EDGE模式

OPPOSITE_EDGE 模式

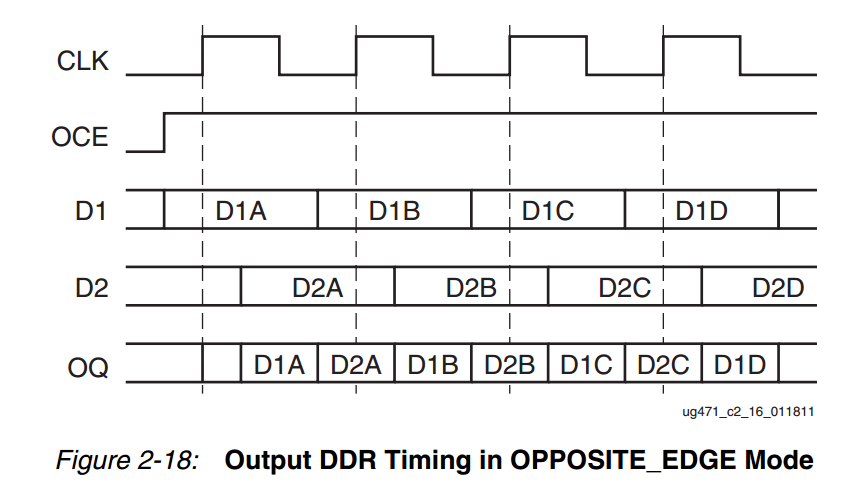

在此模式中,時鐘邊沿被用來以兩倍的吞吐量從FPGA邏輯中捕獲資料。這種結構與virtex-6的實現比較相似。兩個輸出都提供給IOB的資料輸入或者三態控制輸入。使用OPPOSITE_EDGE模式的輸出DDR時序圖如下圖所示:

SAME_EDGE 模式

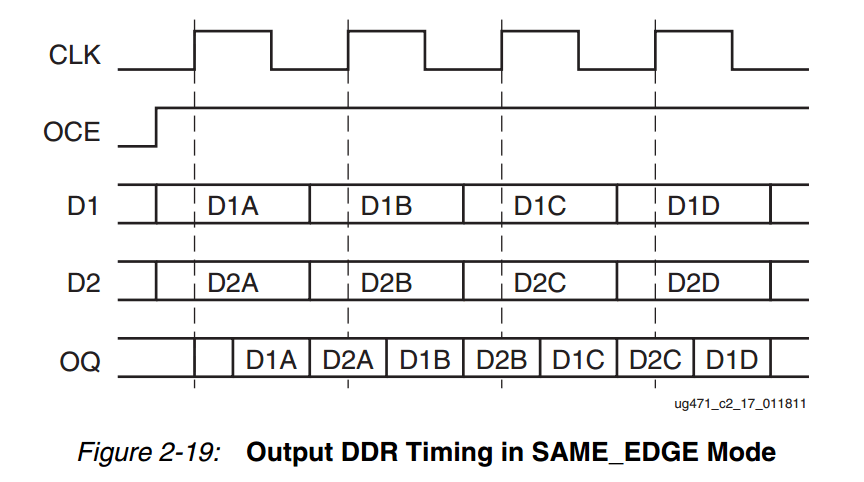

在此模式下,資料可以在相同的時鐘邊沿從給IOB。相同的時鐘沿江資料送給IOB可以避免建立時間違規,並允許使用者使用最小的暫存器來執行更高的DDR頻率來進行暫存器的延遲,而不是使用CLB暫存器。下圖顯示了使用SAME_EDGE模式的輸出DDR的時序圖:

時鐘前向

輸出DDR可以傳送時鐘的副本到輸出。這對於傳播時鐘和DDR資料之間相同的延時是非常有用的,並且對於多個時鐘生成,每個時鐘負載具有唯一的時鐘驅動器。這是通過將ODDR原語中D1輸入設定為High,D2輸入設定為低來實現的。Xilinx建議使用此方案將FPGA邏輯時鐘轉發到輸出引腳。

輸出DDR原語(ODDR)

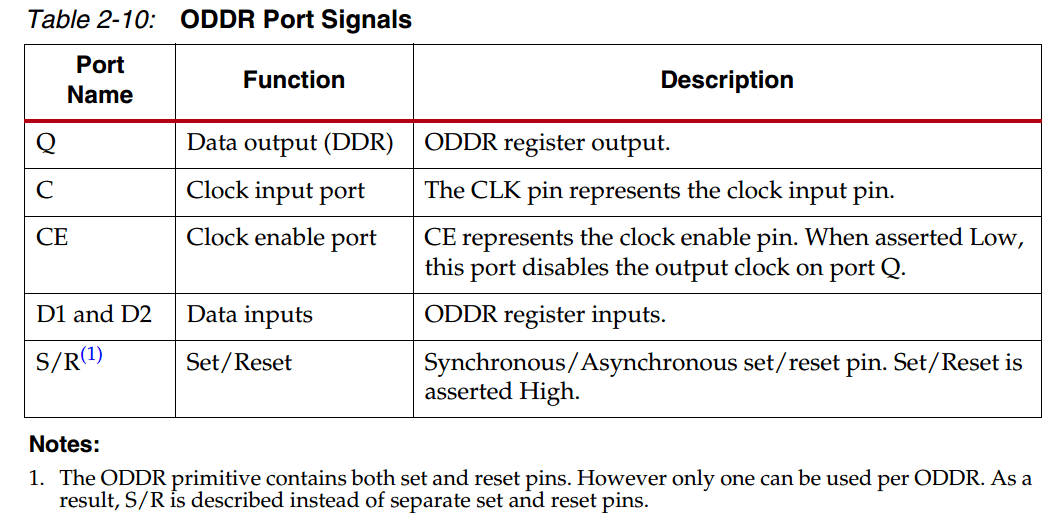

圖2-20顯示了ODDR原語結構圖。Set和Reset不能同時置位。表2-21列出了ODDR埠訊號。表2-11描述了各種可哦那個的屬性和ODDR原語的預設值。

ODDR在verilog中的介面例化

- ODDR #(

- .DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

- .INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

- .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

- ) ODDR_inst (

- .Q(Q), // 1-bit DDR output

- .C(C), // 1-bit clock input

- .CE(CE), // 1-bit clock enable input

- .D1(D1), // 1-bit data input (positive edge)

- .D2(D2), // 1-bit data input (negative edge)

- .R(R), // 1-bit reset

- .S(S) // 1-bit set

- );