xilinx 7系列FPGA配置篇簡介

今天咱們聊聊xilinx7系列FPGA配置的相關內容。總所周知FPGA上電後,其工作的邏輯程式碼需要從外部寫入FPGA,FPGA掉電後其邏輯程式碼就丟失,因此FPGA可以被無限次的配置不同的邏輯程式碼,但FPGA需要配備外部的非易失儲存器來儲存其邏輯程式碼或者通過微控制器、DSP或者其它控制器來實現FPGA上電後的邏輯程式碼載入。

xilinx7系列FPGA設計有專門的邏輯程式碼配置管腳,通過不同的管腳接法,其邏輯程式碼配置模式可以分為以下7種:

1,主串配置模式

2,從串配置模式

3,主並配置模式

4,從並配置模式

5,JTAG配置模式

6,主SPI配置模式

7,主BPI配置模式

所謂的主,即配置時鐘CCLK由FPGA提供;所謂從,即配置時鐘CCLK由外部控制器提供。下面這張表代表了這7種配置模式,其模式的切換由FPGA的3個配置管腳M0、M1、M2控制:

下面咱們分別說說xilinx7系列FPGA的這7種配置模式:

1,主串配置模式

在該模式下,FPGA向外部的非易失性序列資料儲存器或者控制器發出CCLK時鐘訊號,配置資料會以序列方式載入FPGA,在前幾代的FPGA中,儲存器通常選擇xilinx 官方的XCF序列系列儲存器,並給出了相應的設計原理圖,但在7系列FPGA中,這種方式貌似被放棄了,其官方的配置文件裡並無主串配置模式的相關詳細描述。

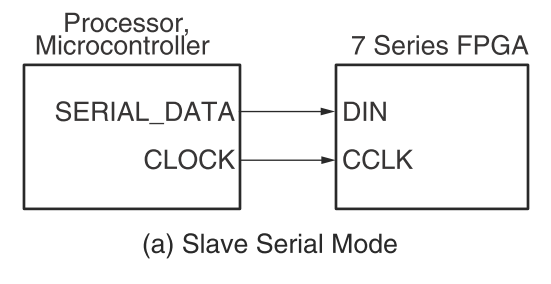

2,從串配置模式

如下圖1所示,在該模式下,由外部的處理器提供CCLK時鐘和序列資料,使用者實現起來相對複雜,不夠大眾化,這裡就不做介紹了。

圖1

3,主並配置模式

同樣的,該模式在其官方文件並無詳細設計描述,無從參考。

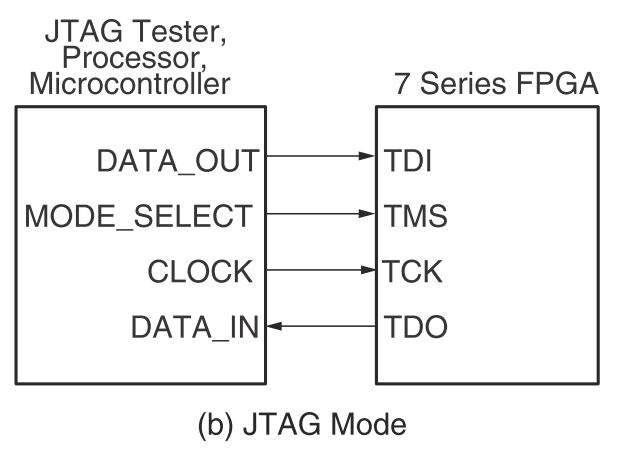

4,從並配置模式

如下圖2所示,在該模式下,外部處理器提供配置時鐘和並行的配置資料,該模式相對於序列方式來說,配置的速度快,但設計稍微複雜。下圖3為官方給出的詳細配置原理圖,該模式同樣使用較少。

圖2

圖3

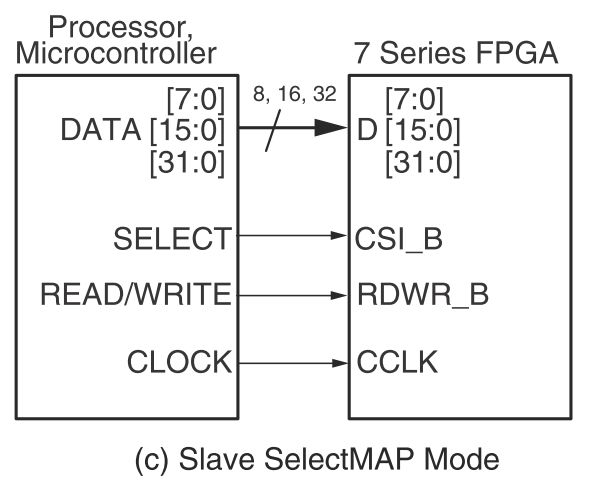

5,JTAG配置模式

如下圖4所示,該模式屬於工程除錯模式,咱們在設計FPGA時必帶這種模式。該模式只能在線配置和除錯FPGA,無法儲存邏輯程式碼。最簡單的操作方式是使用xilinx官方提供的專用JTAG除錯下載器,但同時也允許使用者通過外部處理器自行設計JTAG的資料協議來配置FPGA邏輯程式碼。再次強調,該模式只是一個除錯模式。

圖4

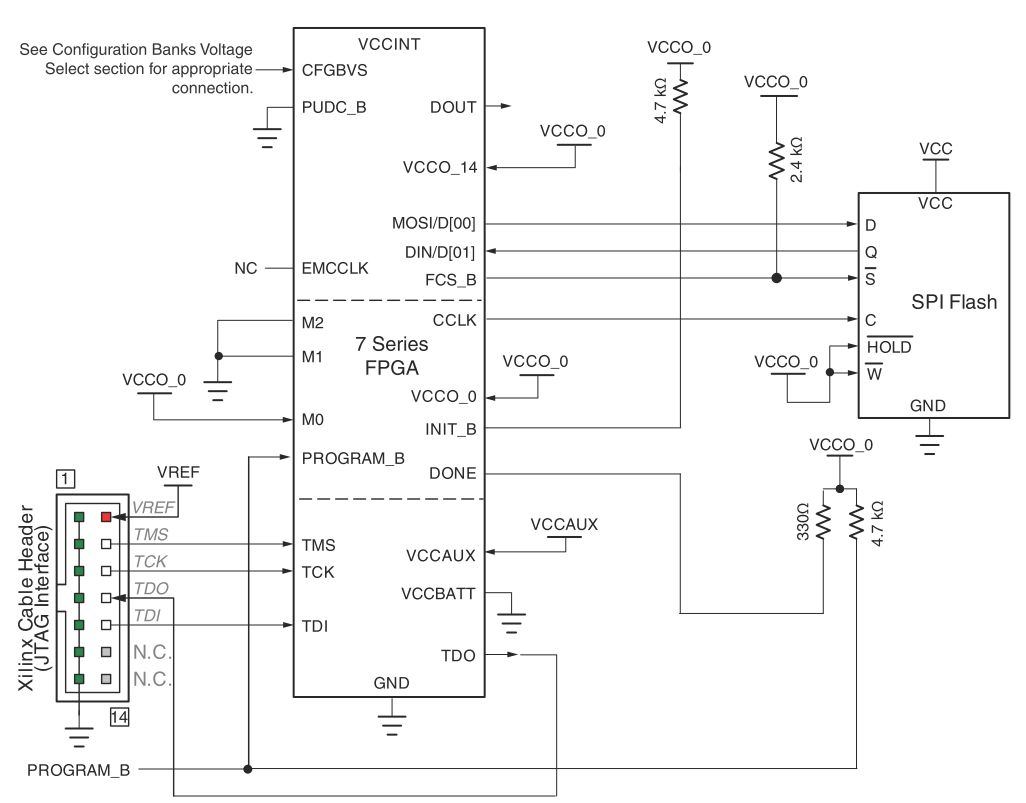

6,主SPI配置模式

這種模式應該算是咱們使用最廣泛的配置模式了,通過外掛一個SPI儲存器即可。通常該模式和JTAG配置模式一起設計。JTAG模式線上除錯好邏輯程式碼後,將該邏輯程式碼儲存在SPI儲存器中,以後FPGA上電後就會自動載入儲存器中的邏輯程式碼。下圖5為官方給出的詳細配置原理圖。

圖5

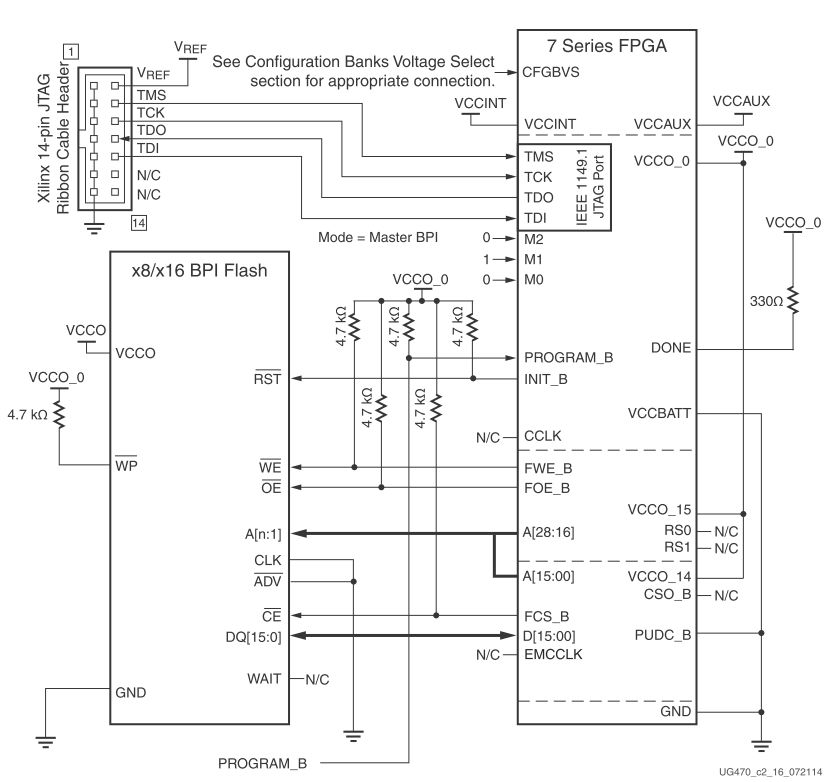

7,主BPI配置模式

該模式的時鐘CCLK同樣由FPGA提供,並行的資料比SPI模式的序列資料配置速度要快,但設計稍微複雜一點。圖6為官方給出的詳細配置原理圖。

圖6

咱們在設計FPGA時,基本上都是採用JTAG配置模式+主SPI配置模式(圖5)或者JTAG配置模式+主BPI配置模式(圖6)。前者用於一般的應用,後者用於對FPGA上電後邏輯程式碼載入速度有較高要求的應用。