Xilinx-7系列FPGA架構學習 --- CLB

Achievement provides the only real pleasure in life.

有所成就是人生唯一的真正的樂趣。

xilinx7系列FPGA主要包括:Spartan®-7/Artix®-7/Kintex®-7/Virtex®-7。其效能/密度/價格也隨著系列的不同而提升。其中以Virtex-7有著極高的系統性能和資源。本篇主要介紹其組成的基本單元configurable logic blocks(CLBs)。通常來說,我們不需要關心或參與邏輯綜合過程CLBs資源的分配。但是如果遇到了效能/時序挑戰的時候,就需要重新審視設計,掌握每一個可利用的資源。比如distributed RAMs和Block RAMs互換(在可替換的前提下)、DSPs與LUT設計等。同時也有助於掌握更深層次的設計,設計出更加合理的HDL程式碼,和XDC約束檔案。

本文主要參考:xilinx官方文件UG474《7 Series FPGAs Configurable Logic Block》和White Paper《Xilinx 7 Series FPGAs:The Logical Advantage》。

CLBs是實現時序邏輯組合邏輯電路的主要邏輯單元。一個CLB由兩個slice組成,而每個slice由4個6輸入LUT、8個FF、複用器和算術進位單元組成。同時SLICE有區分為二:SLICEL和SLICEM(沒有看到縮寫L/M全程,個人認為是Logic和Multiple縮寫,從下面定義可以看出)。大約2/3的是SLICEL(只能用於logic),剩下的是SLICEM(還可以用於distributed RAMs/SRLs32/SRLs16)。每個CLBs是通過Switch Matrix routing,並不是直接互聯。注意到一句話:Four flip-flops per slice (one per LUT) can optionally be configured as

Slices = SliceL + SliceM;SliceL / SliceM = 2;Slices / LUTs = 4;FF / Slices = 8。

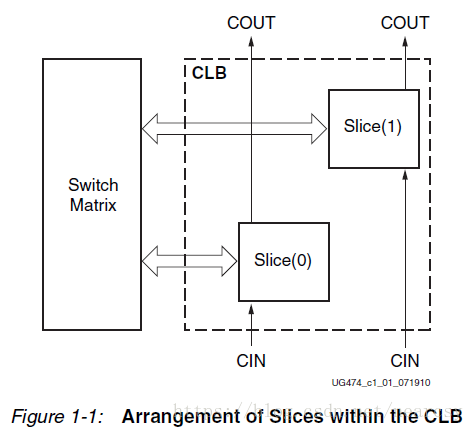

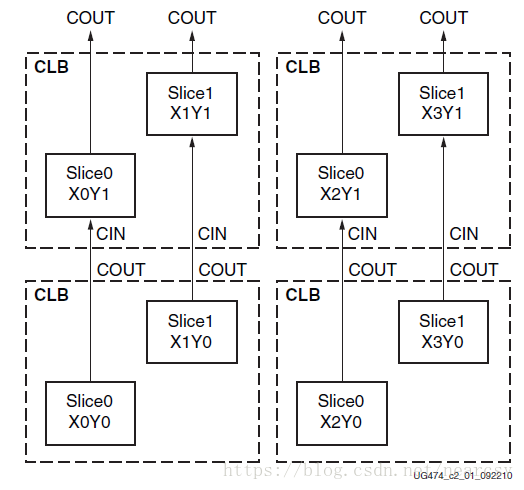

兩個slice分別位於CLB的左列底部和右列頂部。這兩個slice不是直接互聯,而是以列為單位,通過一個獨立的進位鏈(Cout&&Cin)

接。如下圖所示:

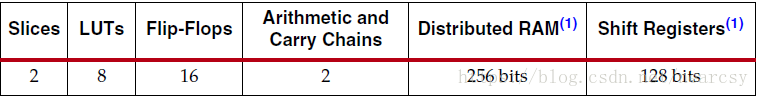

通過以上的分析,每個CLBs具體的資源配置如下:

注意:如前面所述,只有SLICEM可以配置成distributed RAMs和SRLs。

下面文章,將會詳細分析,每個具體的elements的組成、功能細節以及應用。