Xilinx-7系列FPGA架構學習 --- CLB/LUT/...

Achievement provides the only real pleasure in life.

有所成就是人生唯一的真正的樂趣。

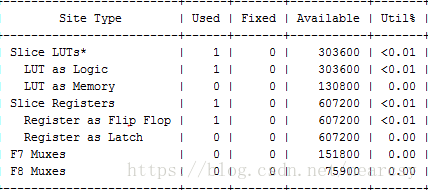

通過xilinx vivado提供給implementment,可以看到實際情況(vivado 2017.4 kintex 7為例):

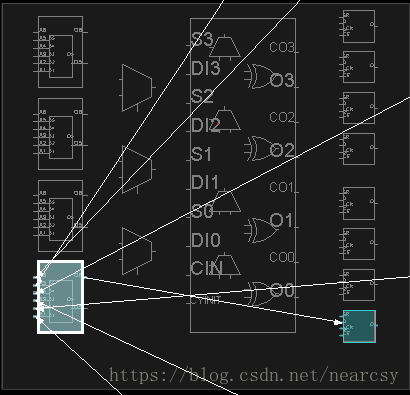

每個CLB包括兩個slice(兩個SLICEL或者一個SLICEM一個SLICEM·)---8個6輸入LUTs(邏輯產生單元),16個FF,以及3個Multiplexer(F7AMUX/F7BMUX/F8MUX)和carry chain組成。

LUT:由6個獨立的輸入A1-A6和兩個獨立的輸出組成O5、O6。

能夠實現:

1. 任意的6輸入布林邏輯:A1-A6作為輸入,O6作為輸出。

2. 兩個5輸入或者更少的:A1-A5作為輸入,A6高,O5和O6作為輸出。

經過LUTs的訊號可以:不做操作(直接出來slice)/從O6出來進入XOR專用門/從O5出來進入進位鏈/接入D觸發器輸入/從O6進入F7AMUX/F7BMUX。F7AMUX和F7BMUX作用是組合4個LUTs,在一個slice中產生任意的7或者8輸入。對於大於8輸入的邏輯,則需要多個slice。值得注意的是對於大於8輸入的多個slice,沒有直接連線在一起。

下面深入理解一下上面文件的含義:

[email protected](posedge sys_clk) begin case(key_in) 6'b000_001: key_edge <= 1'b1; 6'b000_010: key_edge <= 1'b0; 6'b000_100: key_edge <= 1'b1; 6'b001_000: key_edge <= 1'b0; 6'b010_000: key_edge <= 1'b1; 6'b100_000: key_edge <= 1'b0; default:key_edge <= 1'b1; endcase end

在資源報告中,只佔用了一個LUT和1一個FF。可以看出,7series的fpga的確是6輸入的LUT(A1-A6),輸出O6,直接接在FF上。

相關推薦

Xilinx-7系列FPGA架構學習 --- CLB/LUT/...

Achievement provides the only real pleasure in life.有所成就是人生唯一的真正的樂趣。通過xilinx vivado提供給implementment,可以看到實際情況(vivado 2017.4 kintex 7為例):每個C

Xilinx-7系列FPGA架構學習 --- CLB

Achievement provides the only real pleasure in life.有所成就是人生唯一的真正的樂趣。xilinx7系列FPGA主要包括:Spartan®-7/Arti

Xilinx-7系列FPGA架構學習 --- 深入理解LUT

Achievement provides the only real pleasure in life.有所成就是人生唯一的真正的樂趣。LUT的一個重要功能是邏輯函式發生器。本質上,邏輯函式發生器儲存的是真值表(Truth Table)的內容,而真值表則是通過布林表示式獲得。

Xilinx-7系列FPGA架構—— CLB

xilinx7系列FPGA主要包括:Spartan®-7/Artix®-7/Kintex®-7/Virtex®-7。其效能/密度/價格也隨著系列的不同而提升。其中以Virtex-7有著極高的系統性能和資源。本篇主要介紹其組成的基本單元configurable

xilinx 7系列FPGA之電源簡介

前幾篇咱們說了FPGA內部邏輯,本篇咱們再聊一聊7系列FPGA的供電部分。 首先咱們說spartan7系列,通常咱們需要使用以下電源軌: 1, VCCINT FPGA內部核心電壓。其不損壞FPGA器件的

xilinx 7系列FPGA之SelectIO(3)_高階IO邏輯資源簡介

上一篇咱們介紹了IO邏輯資源,本篇咱們來聊一聊高階的IO邏輯資源,即ISERDESE2模組和OSERDESE2模組。 所謂ISERDESE2模組,即Input serial-to-parallel converters。該模組的作用就是實現高速源同步輸入資料的串並轉換。

xilinx 7系列FPGA之SelectIO 篇(1)_IO介面簡介

從本篇開始的接下來共三篇,咱們聊一聊xilinx 7系列FPGA的SelectIO。所謂SelectIO,就是I/O介面以及I/O邏輯的總稱。SelectIO 篇可以分成3部分:第1部分介紹I/O的電氣特性,第2部分介紹I/O邏輯資源,第3部分介紹高階的I/O邏輯資源(serializer/de

xilinx 7系列FPGA配置篇簡介

今天咱們聊聊xilinx7系列FPGA配置的相關內容。總所周知FPGA上電後,其工作的邏輯程式碼需要從外部寫入FPGA,FPGA掉電後其邏輯程式碼就丟失,因此FPGA可以被無限次的配置不同的邏輯程式碼,但FPGA需要配備外部的非易失儲存器來儲存其邏輯程式碼或者通過微控制器、DSP或者其它控制器來

xilinx 7系列FPGA之XADC簡介

今天咱們來聊一聊FPGA裡面的XADC功能。XADC即Xilinx公司的FPGA裡整合的一個ADC模組、溫度感測器、電壓感測器的集合。在7系列FPGA裡,除了少數spartan系列的低端FPGA沒有XADC外,其它所有的7系列FPGA裡都有XADC模組。 XADC包含2個通道的模擬差分輸入、

xilinx 7系列FPGA之儲存器篇簡介

上一篇咱們說了slice,提到了其與全域性時鐘在一起就可以實現任意的組合邏輯和時序邏輯功能,但很多時候咱們還需要將FPGA內部的資料暫時儲存,用作它用。Slice作為FPGA最基本的單元,也是能夠完成資料儲存的功能,但顯然有些大材小用,因此xilinx公司在其FPGA內部專門集成了很多儲存器模組

xilinx 7系列FPGA之slice篇簡介

xilinx 7系列FPGA之slice篇簡介 Xilinx的官方文件在介紹FPGA的邏輯資源時通常是按照CLB(Configurable Logic Block)來介紹,把CLB作為FPGA裡的最小邏輯單元。但是CLB是由2個slice構成,因此平時大家都把slice掛嘴邊,稱為最

xilinx 7系列FPGA時鐘篇(4)_CMT簡介

xilinx 7系列FPGA時鐘篇(4)_CMT簡介 上篇咱們僅僅簡要的介紹了時鐘的用法,並未詳細的說明,主要是因為很多時鐘用法是針對特定的應用需求,無法一一介紹。本篇咱們將重提上篇的CMT時鐘模組,聊一聊它的用法。可以這麼說,每個靠譜的FPGA應用裡都應該用到CMT模組。 在7

xilinx 7系列FPGA時鐘篇(3)_時鐘操作法則

xilinx 7系列FPGA時鐘篇(3)_時鐘操作法則 上一篇咱們介紹了7系列FPGA的時鐘區域內部結構,本篇咱們接著介紹如何實際操作時鐘。不說其它的,直接先上兩張圖,大家如果能看懂這兩張圖,那麼就不用浪費時間看我接下來的廢話了。。。。。 C:被外部差分/單端時鐘驅動;可

xilinx 7系列FPGA時鐘篇(2)_時鐘區域簡介

xilinx 7系列FPGA時鐘篇(2)_時鐘區域簡介 上一篇咱們介紹了7系列FPGA的整體時鐘架構,知道了FPGA是由很多個時鐘區域組成,時鐘區域之間可以通過Clock Backbone 和CMT Backbone來統一工作。本篇咱們就說一下時鐘區域的內部結構,如圖1所示的虛線框內

xilinx 7系列FPGA時鐘篇 (1)_時鐘結構簡介

xilinx 7系列FPGA時鐘篇 (1)_時鐘結構簡介 說起xilinx的FPGA時鐘結構,7系列FPGA的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如圖1所示,理解了這張圖,咱們就對七系列的FPGA時鐘結構瞭如指掌,下面咱們就聊聊這張圖: 1,Cloc

xilinx 7系列FPGA分類簡介

xilinx 7系列FPGA分類簡介 賽靈思公司的7系列FPGA根據不同客戶的應用需求,分為4個子系列,即Spartan7系列、Artix7系列、Kintex7系列以及Virtex7系列。和前幾代FPGA產品不同的是,7系列FPGA採用的是統一的28nm設計架構,客戶在不同子系列的使

xilinx 7系列FPGA分類簡介(轉)

xilinx 7系列FPGA分類簡介 賽靈思公司的7系列FPGA根據不同客戶的應用需求,分為4個子系列,即Spartan7系列、Artix7系列、Kintex7系列以及Virtex7系列。和前幾代FPGA產品不同的是,7系列FPGA採用的是統一的28nm設計架構

FPGA block RAM和distributed RAM區別(以及xilinx 7系列CLB資源)

區別之1block ram 的輸出需要時鐘,distributed ram在給出地址後既可輸出資料。區別之2distributed ram使用更靈活方便些區別之3block ram有較大的儲存空間,distributed ram浪費LUT 資源補充:1,物理上看,block

FPGA開發筆記(xilinx 7系列)

本人才疏學淺,孤陋寡聞,下文若有不當之處,還請賜教 一、verilog注意點 延時語句 begin areg = breg; #10 creg = areg; //在兩條賦值語句間延遲10個時間單位。 end 2.觸發事件 para

FPGA基礎知識24(xilinx 高速收發器系列:Xilinx 7 系列的時鐘資源(1))

談到數字邏輯,談到FPGA設計,每位工程師都離不開時鐘。這裡我們簡單介紹一下xilinx 7 系列中的時鐘資源。時鐘設計的好壞,直接影響到佈局佈線時間、timing的收斂情況,FPGA的時鐘設計非常重要,認識FPGA的時鐘資源很有必要。 FPGA設計是分模組的,