【 Vivado 】基本的時序約束、分析的概念

目錄

時序路徑:

關於時序路徑,曾也有幾篇博文講到:【 FPGA 】時序分析中的基本概念和術語

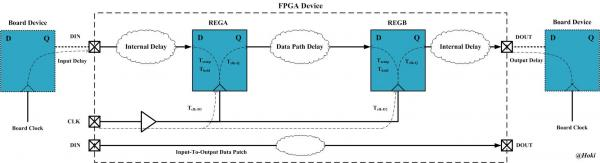

時序路徑分為四種,下面這張圖明明白白我的心。

圖1中包含了主要的時序分析路徑:

1. 輸入埠到FPGA內部時序單元的路徑

2. FPGA內部時序單元間的路徑

3. FPGA內部時序單元到輸出埠的路徑

4.

(圖1)(看不清看開頭的第一張圖)

不管時序單元是在FPGA內部還是外部,除了第4條路徑,它是從輸入埠到輸出埠,其間沒有鎖存,其它3條路徑的時序分析都以2個時序單元間的路勁進行分析,如圖2所示。

(圖2)

第一個時序單元上的時鐘稱為source clock(啟動時鐘),第二個時序單元上的時鐘稱為destination clock(鎖存時鐘),時序分析從source clock的上升沿開始,到之後的destination clock的上升沿結束,時序分析的過程就是檢驗資料在兩個上升沿時間差內經過資料路徑傳輸後是否滿足要求,資料到達時需要滿足後一級時序單元的setup

Clock Setup Check:

檢驗Setup是否滿足要求,這邊引入setup slack概念,只要setup slack的值大於零即Setup檢查滿足要求,其計算公式如下:

setup slack = data required time – data arrival time

其中:

data required time=destination clock edge time + destination clock path delay- clock uncertainty- setup time

data arrival time = source clock edge time + source clock path delay+ clock to output time + data path delay

公式代入可得到:

setup slack = (destination clock edge time - source edge time)+ (destination clock path delay - source clock path delay)

- clock uncertainty - setup time - clock to output time - data path delay

= Tdestination_to_source + (Tclk-D2 – Tclk-D1) – Tclk_uncertainty – Tsetup – uTco - Tdata_path_delay

在Setup檢查中source clock一定超前於destination clock。

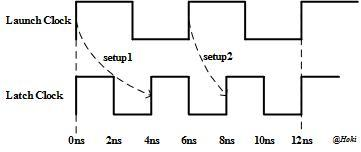

其中第一部分Tdestination_to_source,當source clock和destination clock為非同步時鐘時,如圖3中例項,source clock的週期等於6ns,destination clock的週期等於4ns,首先假定2個時鐘的相位差為0,圖中在這種情況下有2個setup關係,setup1下Tdestination_to_source = 4ns,setup2下Tdestination_to_source = 2ns,在實際分析中應該選取最嚴格的情況,即選取setup2這種。

(圖3)

而當source clock和destination clock為同一個時鐘時,Tdestination_to_source的值很顯然就是時鐘週期Tclk_period,這也是時序分析最多的情況了,進一步推導

setup slack = Tclk_period+ (Tclk-D2– Tclk-D1) – Tclk_uncertainty - Tsetup – Tdata_path_delay > 0,可以得到:

Tclk_period > Tclk_uncertainty + Tsetup + Tdata_path_delay - (Tclk-D2 – Tclk-D1)

Tclk_period、Tclk_uncertainty可以通過時序約束確定其值,uTco, Tsetup是時序單元的屬性值,(Tclk-D2 – Tclk-D1)在佈局佈線後其值也能確定,剩下Tdata_path_delay對Tclk_period影響最大,一個設計Setup檢查中的關鍵路徑往往是Tdata_path_delay值最大的一條路徑,影響其值有很多原因,如邏輯級數過多,扇出導致佈線延時過大…

Clock Hold Check:

對應Hold檢查,也有hold slack,其計算公式如下:

hold slack = data arrival time – data required time

其中

data required time = destination clock edge time + destination clock path delay + clock uncertainty + hold time

data arrival time = source edge time + source clock path delay+ clock to output time + data path delay

代入公式得到:

hold slack = (source clock edge time - destination edge time)+(source clock path delay - destination clock path delay)

- clock uncertainty - hold time + clock to output time + data path delay

=Tsource_to_destination + (Tclk-D1 – Tclk-D2) – Tclk_uncertainty – Thold + uTco + Tdata_path_delay

與Setup檢查不同,在Hold檢查下destination clock超前於source clock。在Setup檢查中,Tdestination_to_source的值選取destination clock和source clock相差最小的情況下進行分析;而Hold檢查中Tsource_to_destination的值選取所有Setup關係分別進行分析,每一種Setup關係對應有兩種情況,然後選取所有情況中Tdestination_to_source值大的計算對應的Tsource_to_destination

a. 取Setup關係的前一個destination clock沿,如圖4中Hold1a和Hold2a

b. 取Setup關係的destination clock沿,如圖4中Hold1b和Hold2b

(圖4)

根據圖4中例項計算得到:

Hold1a:Tdestination_to_source= 0ns

Hold1b:Tdestination_to_source= -2ns

Hold2a:Tdestination_to_source= -2ns

Hold2b:Tdestination_to_source= -4ns

顯然選取Hold1a,對應Tsource_to_destination值為0ns

當source clock和destination clock為同一個時鐘時,可以計算得到:

Tsource_to_destination值為0ns,進一步推導

hold slack = Tsource_to_destination + (Tclk-D1 – Tclk-D2) – Tclk_uncertainty – Thold+ Tdata_path_delay > 0可以得到:

Tdata_path_delay >Tclk_uncertainty + Thold + (Tclk-D2 – Tclk-D1)

由上得出資料路徑的延時也不能過短,與Setup檢查是矛盾對立的存在;在FPGA設計或者數字前端開發時,工程師考慮最多的是Setup是否滿足要求,而Hold檢查的工作主要交給工具或者負責數字後端的工程師解決。

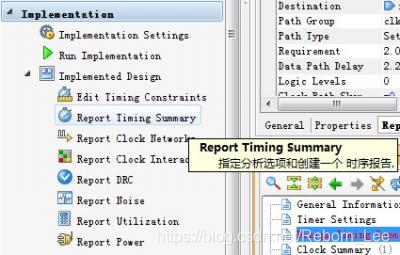

Timing Report in Vivado:

下面通過簡單的例項說明一下vivado中的時序分析,當FPGA設計經過綜合實現後,通過Report Timing Summary開啟時序報告,如圖5、6所示。

(圖5)

(圖6)

圖中有紅色部分表示設計中有時序不滿足要求,此例中是Setup。選擇Setup中未滿足要求的Path,開啟Path Properties,如圖7所示。

(圖7)

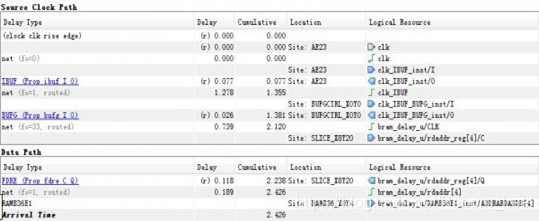

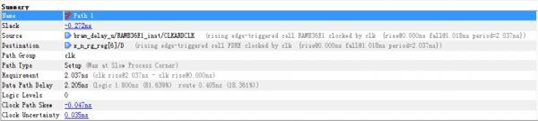

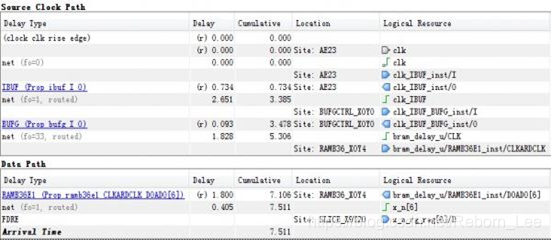

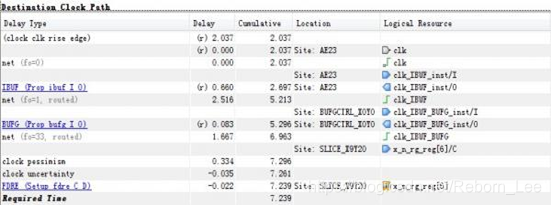

Setup關鍵路徑的時序報告如圖8所示,報告由四部分組成:Summary, Source Clock Path, Data Path和Destination Clock Path,其中由Source Clock Path和Data Path得出Arrival Time,由Destination Clock Path得出Required Time。

(圖8)

Hold檢查的報告也類似,如圖9所示。