【 Vivado 】XDC檔案的約束順序

由於XDC約束是按順序應用的,並且基於明確的優先順序規則進行優先順序排序,因此必須仔細檢查約束的順序。

如果多個物理約束髮生衝突,則最新約束將獲勝。 例如,如果通過多個XDC檔案為I / O埠分配了不同的位置(LOC),則分配給該埠的最新位置優先。

Vivado IDE可全面瞭解您的設計。 要逐步驗證您的約束:

1.執行相應的報告命令。

2.檢視Tcl控制檯或“訊息”視窗中的訊息。

推薦的約束順序

建議:無論是為設計使用一個還是多個XDC檔案,都按以下順序組織約束。

## Timing Assertions Section

# Primary clocks

# Virtual clocks

# Generated clocks

# Clock Groups

# Bus Skew constraints

# Input and output delay constraints

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

## Physical Constraints Section

# located anywhere in the file, preferably before or after the timing constraints

# or stored in a separate constraint file

從時鐘定義開始。 必須先建立時鐘,然後才能將它們用於任何後續約束。 宣告之前對時鐘的任何引用都會導致錯誤,並忽略相應的約束。 在單個約束檔案中以及設計中的所有XDC檔案(或Tcl指令碼)中都是如此。

約束檔案的順序很重要。 您必須確保每個檔案中的約束不依賴於另一個檔案的約束。 如果是這種情況,則必須最後讀取包含約束依賴項的檔案。 如果兩個約束檔案具有相互依賴關係,則必須將它們手動合併到一個包含正確序列的檔案中,或者將檔案分成幾個單獨的檔案並正確排序。

編輯約束順序

Vivado IDE約束管理器將任何已編輯的約束儲存回XDC檔案中的原始位置,但不會儲存在Tcl指令碼中。 任何新約束都儲存在標記為目標的XDC檔案的末尾。 在許多情況下,當約束集包含多個XDC檔案時,目標約束檔案不是列表中的最後一個檔案,並且在開啟或重新載入設計時不會最後載入。 因此,儲存在磁碟上的約束序列可能與之前在記憶體中的約束序列不同。

重要資訊:您必須驗證儲存在約束檔案中的最終序列是否仍按預期工作。 如果必須修改序列,則必須通過直接編輯約束檔案來修改它。 這對時序約束尤為重要。

約束檔案順序

在沒有任何IP的專案流程中,所有約束都位於約束集中。 預設情況下,Vivado IDE中顯示的XDC檔案(或Tcl指令碼)的順序定義了將elaborated design或synthesized design載入到記憶體時工具使用的讀取順序。 首先讀取列表頂部的檔案,最後讀取底部的檔案。 您只需在IDE中選擇檔案並將其移動到列表中的所需位置即可更改順序。

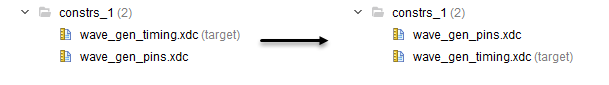

例如,在圖1中,使用拖放操作將檔案wave_gen_pin.xdc移動到檔案wave_gen_timing.xdc之前。

Figure 1: Changing XDC File Order in the Vivado IDE Example

The equivalent Tcl command is:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

在非專案模式下,read_xdc呼叫的順序決定了約束檔案的計算順序。

Constraint Files Order with IP Cores

許多IP核心隨附一個或多個XDC檔案。 在RTL專案中生成此類IP核心時,還會在各種設計編譯步驟中使用其XDC檔案。

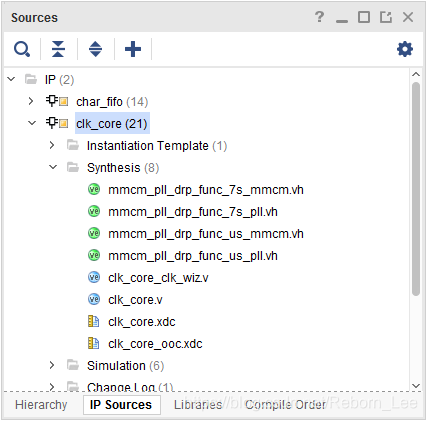

例如,圖2顯示專案中的一個IP核帶有一個XDC檔案。

Figure 2: XDC Files in the IP Sources

預設情況下,在使用者XDC檔案之前讀入IP XDC檔案。 以這種方式處理它允許IP建立可在XDC中引用的時鐘物件。 它還允許您覆蓋由IP核心設定的物理約束,因為在IP之後評估使用者約束。 對於依賴於由使用者或其他IP建立的時鐘物件的IP核,此順序有一個例外(例如,get_clocks -of_objects [get_ports clka])。 在這種情況下,在使用者檔案之後讀取IP XDC。

此行為由PROCESSING_ORDER屬性控制,為每個XDC檔案設定:

•EARLY:必須先讀取的檔案

•NORMAL:預設

•LATE:必須最後讀取的檔案

IP XDC將其PROCESSING_ORDER屬性設定為EARLY或LATE。 沒有哪個 IP提供屬於NORMAL約束組的XDC檔案。 對於屬於同 一PROCESSING_ORDER組的使用者XDC(或Tcl)檔案,Vivado IDE中顯示的相對順序決定了它們的讀取順序。 可以通過移動Vivado IDE約束集中的檔案或使用reorder_files命令來修改組中的順序。

對於屬於同一PROCESSING_ORDER組的IP XDC檔案,順序由IP核心的匯入或建立順序確定。 建立專案後,無法更改此順序。

最後,使用者組和IP XDC PROCESSING_ORDER組之間的相對順序如下:

1.標記為EARLY的使用者約束

2.標記為EARLY的IP約束(預設)

3.標記為NORMAL的使用者約束

4.標記為LATE的IP約束(包含時鐘依賴性)

5.標記為LATE的使用者約束

注意:將其PROCESSING_ORDER設定為LATE(以便在使用者約束後進行處理)的IP XDC檔案命名為<IP_NAME> _clocks.xdc。

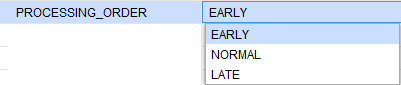

下圖顯示瞭如何設定PROCESSING_ORDER屬性的示例:

Figure 3: Setting the XDC File PROCESSING_ORDER Example

The equivalent Tcl command is:

set_property PROCESSING_ORDER EARLY [get_files wave_gen_pins.xdc]

建議:使用Tcl控制檯中的report_compile_order -constraints命令報告由工具根據上述屬性確定的XDC檔案讀取順序,包括IS_ENABLED,USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION。

Changing Read Order

要在約束集中更改XDC檔案或非託管Tcl指令碼的讀取順序,請執行以下操作:

1.在“源”視窗中,選擇要移動的XDC檔案或Tcl指令碼。

2.將檔案拖放到約束集中的所需位置。

對於圖1中所示的示例,等效的Tcl命令是:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] [get_files wave_gen_pins.xdc]

在非專案模式下,read_xdc或source命令的順序決定了約束檔案的讀取順序。

如果使用帶有約束的IP核心,則會自動處理兩組約束,如下所示:

•不依賴於時鐘的約束被分組到XDC檔案中,PROCESSING_ORDER設定為EARLY,

•依賴於時鐘的約束在PROCESSING_ORDER設定為LATE的XDC檔案中分組。

預設情況下,使用者XDC檔案屬於PROCESSING_ORDER NORMAL組。 它們在EARLY XDC檔案之後和LATE XDC檔案之前載入。 對於每個PROCESSING_ORDER組,IP XDC檔案的載入順序與IP Sources視窗中IP核的列表順序相同。 例如,下圖顯示了XDC檔案附帶的專案IP核心之一。

Figure 4: XDC Files in the IP Sources

開啟設計時,日誌檔案顯示最後載入了IP XDC檔案:

Parsing XDC File[C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst'

Finished Parsing XDC File

[C:/project_wave_gen_hdl.srcs/sources_1/ip/clk_core/clk_core.xdc] for cell 'clk_gen_i0/clk_core_i0/inst'

Parsing XDC File

[C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0'

Finished Parsing XDC File

[C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo.xdc] for cell 'char_fifo_i0/U0'

Parsing XDC File

[C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc]

Finished Parsing XDC File

[C:/project_wave_gen_hdl.srcs/constrs_1/imports/verilog/wave_gen_timing.xdc]

Parsing XDC File

[C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0'

Finished Parsing XDC File

[C:/project_wave_gen_hdl.srcs/sources_1/ip/char_fifo/char_fifo/char_fifo_clocks.xdc ] for cell 'char_fifo_i0/U0'

Completed Processing XDC Constraints

與使用者XDC檔案不同,您無法直接更改屬於同一PROCESSING_ORDER組的IP XDC檔案的讀取順序。 如果必須修改訂單,請執行以下操作:

1.禁用相應的IP XDC檔案(IS_ENABLED設定為false)。

2.複製他們的內容。

3.將內容貼上到約束集中包含的一個XDC檔案中。

4.在需要的地方使用完整的分層網表物件路徑名更新複製的IP XDC命令。 這樣做是必需的,因為IP XDC約束以這樣的方式編寫,即它們可以作用於IP例項。

5.檢視以特殊方式處理範圍約束的get_ports查詢。