電路相關----積分電路電容上並電阻的作用

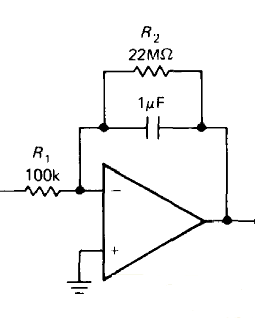

在書(The Art of Electronics)上看到“If the residual drift of the integrator is still too large for a given application, it may be necessary to put a large resistor R2 across C to provide dc feedback for stable biasing.”

如果積分器的殘餘漂移仍然過大,對於一個給定的應用程式,可能有必要把一個大的電阻器R2電容 C的兩端,以提供穩定的偏置直流反饋。

意思是可以增大R2和C的值,達到穩定的偏置電流。

文中主要是說明偏置的,加上R2後,運放有直流反饋,對穩定有益。

可以這樣想,運放的放大倍數是非常大的,它對直流至截止頻率處的訊號都有同樣的放大量,

如果沒有R2時,可以理解為直流放大量為無窮大,那麼,運放稍有點失調什麼的,就會使輸出電平在電源電壓或者0電平

相關推薦

電路相關----積分電路電容上並電阻的作用

在書(The Art of Electronics)上看到“If the residual drift of the integrator is still too large for a given application, it may be necessary to p

為什麼在晶振上並電阻?

一般接crystal內部的晶片電路,原理上就是一個非閘電路,非門在微觀電路上可以看成一個增益個別大的放大器,接一個電阻,你可以看作是反饋電阻,它的作用是讓震盪器更加穩定的工作。這個電阻是為了使本來為邏輯反相器的器件工作線上性區, 以獲得增益, 在飽和區是沒有增益的, 而沒有

電路相關----實際積分電路

實際積分電路由圖5.4-6B看出,曲線1為理想積分電路的特性曲線,曲線2為實際積分電路的特性曲線。特性曲線2不能保持線性增長,輸出電壓UO在到達UOM(運放輸出電壓負向飽和值)以後,如果U1不變,曲線2與曲線1的偏離越來越嚴重,形成很大的積分誤差,甚至不能正常工作。因此圖5.

【硬體】在電路中電阻的兩端並聯一個電容,或者電容一端接電阻,一端接地,這兩種情況電容分別起什麼作用

一、對於電子電路: 電阻的兩端並聯一個電容,為了減小對高頻訊號的阻抗,相當於微分,這樣訊號上升速度加快,用於提高響應速度;電容一端接電阻,一端接地,則相反,濾去高頻,相當於積分,用於濾波。 最典型的應用就是放大電路中的高低音訊控制。 二、對於電力電路: 不管RC串聯還

不要告訴我你懂上拉電阻,OC,OD電路

一.介面相關電路及概念 1.集電極開路輸出(oc) 當三級管集電極什麼都不接,叫做集電極開路,左側的三極體用於反向作用。 1)當左側輸入0時,左側三極體截止,VCC通過電阻加到右側三極體基極,右測輸出端連線到地,輸出“0” 2)因為集電極開路是無法輸出高電平的,如果想輸出

BUCK電路中的BOOT電容

BUCK電路一種開關電源,其由高管與低管輪流導通進行降壓。一般的其拓撲結構如下: 當VCC電壓與VO電壓接近時,高管的VGS過小使得高管無法開啟。 對於MOSFET,導通的條件是柵-源極之間的電壓(Ugs)大於某個閥值,這個閥值不同的管其值不盡相同。下圖所示是一個NMOS的半橋,對於低端的管

雷擊浪湧抑制電路設計---放電管、壓敏電阻、TVS管

雷電壓/電流的特性 1.2/50uS雷電壓脈衝波形(IEC61000-4-5) 1.2/50uS雷電壓脈衝波形(IEC61000-4-5) 雷擊浪湧防護器件各自的優缺點 氣體放電管 半導體放電管 壓敏電阻 TVS 防雷模組(SPD) 氣體放電管

關於隔直電路中隔直電容的正確應用

經常看到用一個電容做成的所謂的“隔直電路”,如圖1。這是沒真正理解隔直的含義的表現。電容可以實現隔直,這是中學生的理解水平,搞電子的人不應該停留在這個水平。 這世界上並不存在絕對的“隔直流通交流”的電路。試問直流和交流的界限何在?1Hz是交流,0.1Hz是交流……無窮小

完美積分電路設計的理解

我們一說到積分電路,相信大家都很熟悉,腦海裡一定會出現下面的影象: 本文引用地址:http://www.eepw.com.cn/article/269312.htm 以及其典型應用方波變換三角波(紅色為輸入訊號,藍色為輸出訊號)。 同時在計算輸入和輸

電路中串聯 並聯 電阻作用

看電源是什麼型別的。 對於恆壓源,串聯電阻可以起到限流及降壓的作用。並聯電阻時,由於電源的內阻基本為0,對並聯前的支路不起作用。比如家中的供電電源就是恆壓源。你開一個電燈,與開10個電燈相比,燈都一樣亮,因為並聯電流中的電壓都是相同的,變化的只是總電流(等於並聯各支路電流之和)。 恆壓源在開路時

基本RC積分電路及原理分析

電阻R和電容C串聯接入輸入訊號VI,由電容C輸出訊號V0,當RC (τ)數值與輸入方波寬度tW之間滿足:τ>>tW (一般至少為10倍以上),這種電路稱為積分電路 在電容C兩端(輸出端)得到鋸齒波電壓,如圖6所示: 1) t=t1 時

上拉電阻和下拉電阻

集成 條件 基本上 作用 輸出 設置 alt 上拉 com 所謂上。就是指wd=%E9%AB%98%E7%94%B5%E5%B9%B3&hl_tag=textlink&tn=SE_hldp01350_v6v6zkg6">高電平;所謂下,是指wd=%E

Altera FPGA管腳弱上拉電阻詳細設置方法

ssi 彈出 gpo 由於 上拉 tps roman mes src Altera FPGA管腳弱上拉電阻的軟件設置方法 在使用 Altera 的 FPGA 時候, 由於系統需求, 需要在管腳的內部加上上拉電阻。 Quartus II 軟件中在 Assignment E

上拉電阻、下拉電阻、拉電流、灌電流、扇出係數等基本概念

在使用數字積體電路時,拉電流輸出和灌電流輸出是一個很重要的概念,例如在使用反向器作輸出顯示時,圖1是拉電流,即當輸出端為高電平時才符合發光二極體正向連線的要求,但這種拉電流輸出對於反向器只能輸出零點幾毫安的電流用

上拉電阻與下拉電阻講解

輸入 能力 http 高阻 增強 電平 erl 設計 三種 使用原因: 數字電路有三種狀態:高電平、低電平、和高阻狀態,有些應用場合不希望出現高阻狀態,可以通過上拉電阻或下拉電阻的方式使處於穩定狀態,具體視設計要求而定! 一般說的是I/O端口,有的可以設置,有的不可以設置,

【Untiy3d-編輯器相關2】 Inspector上的一些編輯擴充套件

[ContextMenu("Set SomeValue")] void SetSomeValue() { Debug.Log("選中掛有此元件的GameObject的 Inspector面板右鍵,有

微控制器上拉電阻、下拉電阻的詳解和選取

一、定義 1、上拉就是將不確定的訊號通過一個電阻嵌位在高電平!“電阻同時起限流作用”!下拉同理! 2、上拉是對器件注入電流,下拉是輸出電流 3、弱強只是上拉電阻的阻值不同,沒有什麼嚴格區分 4、對於非

初識TensorFlow之將自己訓練好的模型遷移到電腦攝像頭和外接海康攝像頭上,並在視訊中實時檢測

有了訓練好的模型之後,可以將模型遷移到電腦或者手機上 電腦: # -*- coding: utf-8 -*- """ @author: Terry n """ # Imports import numpy as np import os import sys impor

Qt 拖拽圖片到QLabel上並顯示

實現程式碼: #include "mainwindow.h" #include "ui_mainwindow.h" #include <QDragEnterEvent> #include <QDropEvent> #include <QUrl&

數位電路器件——閘電路——與閘電路、或閘電路、非閘電路及例項

閘電路是數位電路中最基本的邏輯單元。它可以使輸出訊號與輸入訊號之間產生一定的邏輯關係。在數位電路中,訊號大都是用電位(電平)高低兩種狀態表示,利用閘電路的邏輯關係可以實現對訊號的轉換。 最基本的閘電路有與閘電路,或閘電路,非閘電路等。 與閘電路 與閘電路