SPI匯流排小結

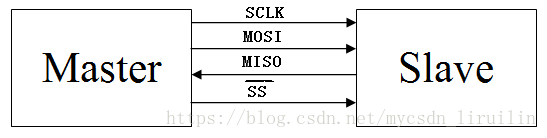

SPI,是英語Serial Peripheral Interface的縮寫,顧名思義就是序列外圍裝置介面。 一、技術性能 SPI介面是Motorola 首先提出的全雙工三線同步序列外圍介面,採用主從模式(Master Slave)架構;支援多slave模式應用,一般僅支援單Master。時鐘由Master控制,在時鐘移位脈衝下,資料按位傳輸,高位在前,低位在後(MSB first);SPI介面有2根單向資料線,為全雙工通訊,目前應用中的資料速率可達幾Mbps的水平。匯流排結構如下圖所示。

二、介面定義 SPI介面共有4根訊號線,分別是:裝置選擇線、時鐘線、序列輸出資料線、序列輸入資料線。

(1)MOSI:主器件資料輸出,從器件資料輸入 (2)MISO:主器件資料輸入,從器件資料輸出 (3)SCLK :時鐘訊號,由主器件產生 (4)/SS:從器件使能訊號,由主器件控制

四、 時鐘極性和時鐘相位 在SPI操作中,最重要的兩項設定就是時鐘極性(CPOL或UCCKPL)和時鐘相位(CPHA或UCCKPH)。時鐘極性設定時鐘空閒時的電平,時鐘相位設定讀取資料和傳送資料的時鐘沿。 主機和從機的傳送資料是同時完成的,兩者的接收資料也是同時完成的。所以為了保證主從機正確通訊,應使得它們的SPI具有相同的時鐘極性和時鐘相位。 SPI介面時鐘配置心得:在主裝置這邊配置SPI介面時鐘的時候一定要弄清楚從裝置的時鐘要求,因為主裝置這邊的時鐘極性和相位都是以從裝置為基準的。因此在時鐘極性的配置上一定要搞清楚從裝置是在時鐘的上升沿還是下降沿接收資料,是在時鐘的下降沿還是上升沿輸出資料。

在這裡插入圖片描述

五、傳輸時序 SPI介面在內部硬體實際上是兩個簡單的移位暫存器,傳輸的資料為8位,在主器件產生的從器件使能訊號和移位脈衝下,按位傳輸,高位在前,低位在後。如下圖所示,在SCLK的下降沿上資料改變,上升沿一位資料被存入移位暫存器。

五、資料傳輸 在一個SPI時鐘週期內,會完成如下操作:

-

主機通過MOSI線傳送1位資料,從機通過該線讀取這1位資料;

-

從機通過MISO線傳送1位資料,主機通過該線讀取這1位資料。 這是通過移位暫存器來實現的。如下圖所示,主機和從機各有一個移位暫存器,且二者連線成環。隨著時鐘脈衝,資料按照從高位到低位的方式依次移出主機暫存器和從機暫存器,並且依次移入從機暫存器和主機暫存器。當暫存器中的內容全部移出時,相當於完成了兩個暫存器內容的交換。

六、優缺點SPI介面具有如下優點: 1) 支援全雙工操作; 2) 操作簡單; 3) 資料傳輸速率較高。同時,它也具有如下缺點:

-

需要佔用主機較多的口線(每個從機都需要一根片選線);

-

只支援單個主機。

-

沒有指定的流控制,沒有應答機制確認是否接收到資料。 **SPI主要特點有:**可以同時發出和接收序列資料;可以當作主機或從機工作;提供頻率可程式設計時鐘;傳送結束中斷標誌;寫衝突保護;匯流排競爭保護等。

-

工作過程: SPI可以用全雙工通訊方式同時傳送和接收8(16)位資料,過程如下:

主機啟動傳送過程,送出時鐘脈衝訊號——>主移位暫存器的資料通過SDO移入到從移位暫存器,同時從移位暫存器中的資料通過SDI移人到主移位暫存器中——>8(16)個時鐘脈衝過後,時鐘停頓,主移位暫存器中的8(16)位資料全部移人到從移位暫存器中,隨即又被自動裝入從接收緩衝器中,從機接收緩衝器滿標誌位(BF)和中斷標誌位(SSPIF)置“1”。同理,從移位暫存器中的8位資料全部移入到主暫存器中,隨即又被自動裝入到主接收緩衝器中.主接收緩衝器滿標誌位(BF)和中斷標誌位(SSPIF)置“1”——>主CPU檢測到主接收緩衝器的滿標誌位或者中斷標誌位置1後,就可以讀取接收緩衝器中的資料。同樣,從CPU檢測到從接收緩衝器滿標誌位或中斷標誌位置1後,就可以讀取接收緩衝器中的資料,這樣就完成了一次相互通訊過程。

SPI匯流排介面及時序

SPI輸出串行同步時鐘極性和相位可以根據外設工作要求進行配置。

若CPOL = 0,串行同步時鐘的空閒狀態為低電平;

若CPOL = 1,串行同步時鐘的空閒狀態為高電平;