ARM CM0 中斷 優先順序

<ARM Cortex-M0權威指南(中文) 高清掃描版.pdf>

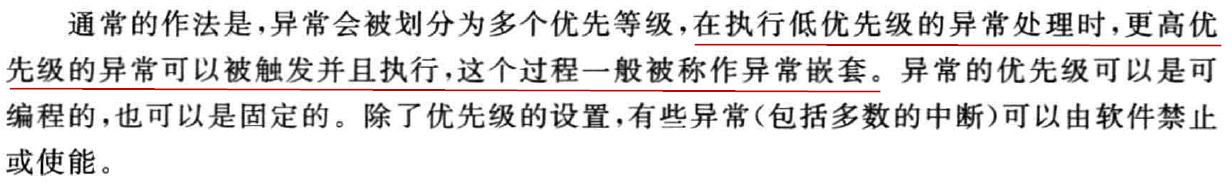

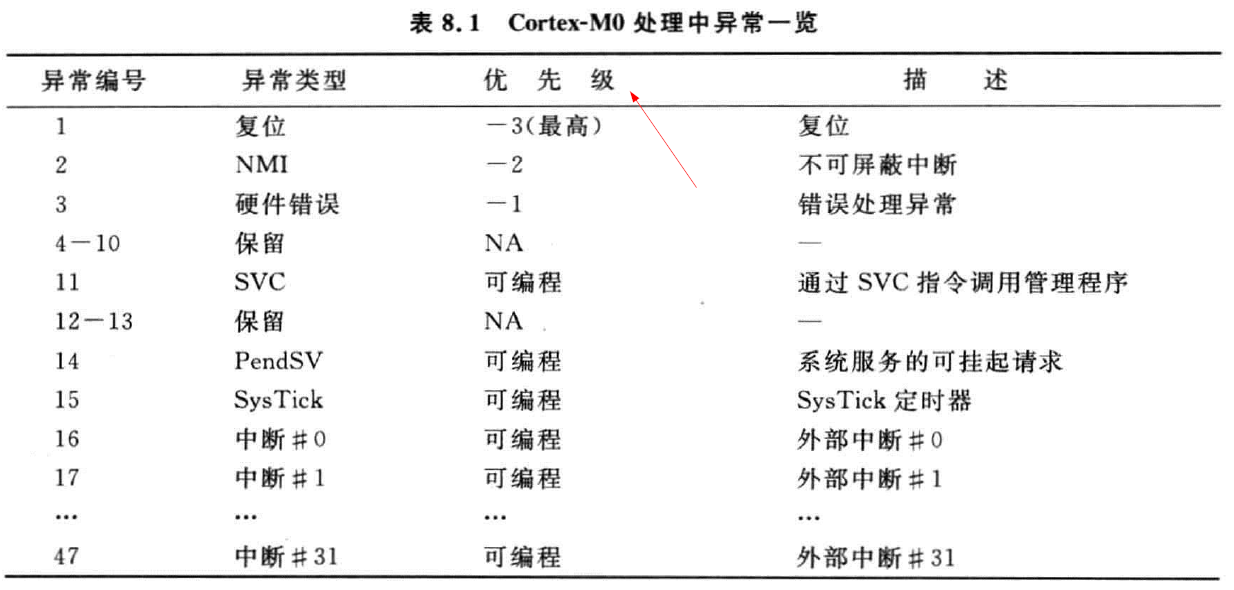

程式設定 使能 中斷A 和中斷B,中斷C,中斷A的優先順序 大於中斷B的優先順序 大於中斷C的優先順序

情況1:

當程式執行過程中,傳送中斷A,進入中斷A的處理函式,

這個時候 如果發生中斷 B,那麼等中斷A的處理函式退出之後,繼續執行中斷B的處理函式。

情況2:

當程式執行過程中,傳送中斷B,進入中斷B的處理函式,

這個時候 如果發生中斷 A,

如果允許中斷巢狀,

如果不允許中斷巢狀

情況3:

當程式執行過程中,傳送中斷B,進入中斷B的處理函式,

這個時候 如果發生中斷 A,

如果允許中斷巢狀,進入中斷A的處理函式,在執行中斷A處理函式過程中,發生中斷C,

中斷A的處理函式 退出之後,怎麼執行 ?

中斷A執行過程中,又有一個比A優先順序還高的中斷髮生怎麼辦 ?

如果不允許中斷巢狀,在執行中斷B的過程中,又產生了中斷C

中斷B的處理函式執行完畢之後,是先執行那個呢?

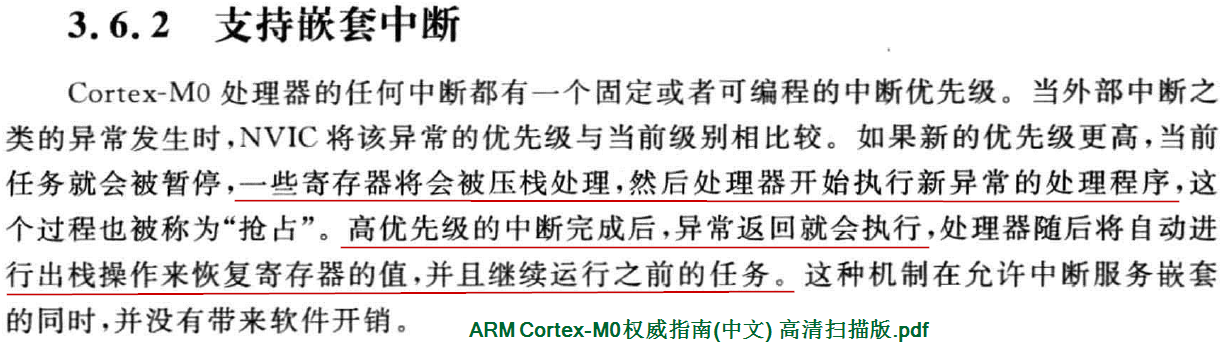

中斷巢狀:

相關推薦

ARM CM0 中斷 優先順序

<ARM Cortex-M0權威指南(中文) 高清掃描版.pdf> 程式設定 使能 中斷A 和中斷B,中斷C,中斷A的優先順序 大於中斷B的優先順序 大於中斷C的優先順序 情況1: 當程式執行過程中,傳送中斷A,進入中斷A的處理函式, 這個時候 如果發生中斷 B,那麼等中

(轉)ARM Linux中斷發生時內核堆棧切換

平臺 晶體 處理器 har 接口 步驟 成了 重要 lin 轉載註明出處:http://www.wowotech.net/forum/viewtopic.php?id=54 對ARM Linux中斷非常簡潔、精確的描述。 發生了中斷,最重要的是保存現場,在中斷處理完之後,

arm gic 中斷控制器工作原理概述

linux pinctrl 裡面有個gpio抽象的中斷控制器與系統的gic中斷控制器級聯cascade 閱讀arm generic interrupter controller architecture specification,總結下 支援的中斷型別 平常工作接觸到的是ppi,

ARM異常 中斷以及他們的向量表分析

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

FreeRTOS 中斷優先順序巢狀錯誤引發HardFault異常解決

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

[原創]NVIC中斷優先順序分組與中斷優先順序和子優先順序

Cortex-M核心提出中斷分組的概念,一共5組 NVIC_PriorityGroup_0 :0 bit 搶佔優先順序 4 bit 子優先順序 NVIC_PriorityGroup_1 :1 bit 搶佔優先順序 3 bit 子優先順序 NVIC_PriorityGroup_2 :2

正點原子 24 NVIC中斷優先順序分組

數值越小,優先順序越高 高優先順序的搶佔優先順序是可以打斷正在進行的低搶佔優先順序中斷的。 搶佔優先順序相同的中斷,高響應優先順序不可以打斷低響應優先順序的中斷。 搶佔優先順序相同的中斷,當兩個中斷同時發生的情況下,哪個響應優先順序高,哪個先執行。 如果兩個中斷的搶佔優先順序和響應優先順序

STM32中斷設定以及中斷優先順序設定

最近,在做一個智慧鎖的專案,由於,今天碰到了一個關於中斷的問題,因此,又回來好好啃一下中斷配置的知識,俗話說:磨刀不誤砍柴工。問題是什麼呢?專案中我用到了一個觸控鍵盤TTP229,結果在測試鍵盤時,不能夠輸入密碼?最終,調試出bug就是由於中斷優先順序的影響。 本專案使用到

ARM的中斷(S3C2440)

中斷要發生需要三部分同時工作: 中斷源 中斷控制器 CPU使能中斷 中斷控制器的作用: 彙集各類中斷訊號併發給CPU。 中斷處理過程: 1.中斷控制器彙集各類中斷訊號併發給CPU。 2.CPU儲存當前程式的執行環境(各個暫存器),呼叫中斷服務程式ISR來處理

STM32 NVIC中斷優先順序

1 NVIC 介紹 STM32 有2 個優先順序:(1)搶佔式優先順序(主優先順序),(2)響應優先順序,每個中斷源都需要指定這兩種優先順序。 1.1 配置 STM32 把 中斷優先順序暫存器變成 4位

3.ARM異常中斷處理及程式設計

ARM異常中斷處理概述: ARM異常中斷處理包括響應中斷、處理中斷、中斷返回等操作。 所以說當ARM異常中斷產生的時候,CPU在執行完當前指令後,PC跳轉到要執行的中斷處理程式處執行,執行完後再返回開

022_STM32中斷優先順序分組解析

(0)STM32有十六個優先順序 (一)STM32分組為:組0-4 (二)分組配置在暫存器SCB->AIRCR中: (三)解析第二點 1. 組0就是4位都用來設定成響應優先順序,2^4=16位都是響應優先順序 2. 組1分為(2^1)兩個搶佔優先順序,在這兩個搶佔優先順序裡面還分別有(2^

STM32中斷優先順序徹底講解

STM32 目前支援的中斷共為 84 個(16 個核心+68 個外部), 16 級可程式設計中斷優先順序 的設定(僅使用中斷優先順序設定 8bit 中的高 4 位)和16個搶佔優先順序(因為搶佔優先順序最多可以有四位數)。 二:優先順序判斷 STM32(Cortex-M3)中有兩個優先順序的概念——搶

STM32學習之路-中斷優先順序

優先順序的問題可以分為以下情況: 搶佔優先順序和響應優先順序 (1)搶佔優先順序高的可以打斷搶佔優先順序低的,形成巢狀. (2)搶佔優先順序相同時,看響應優先順序.如果兩個中斷前後發生的話,後來的中斷不能打斷前一箇中斷 只能等,如果兩個中斷同時發生的話,則響應優先順序高的先

ARM異常中斷處理概述

1.中斷的概念 什麼是中斷,我們從一個生活中的例子引入。你正在家中看書,突然電話鈴響了,你放下書本,去接電話,和來電話的人交談,然後放下電話,回來繼續看你的書。這就是生活中的“中斷”的現象,就是正常的工作過程被外部的事件打斷了。 在處理器中,所謂中斷,是一個過程,即CPU在正常執行程式的過程中,遇到外部/內

ARM GIC 中斷架構

一、前言 GIC(Generic Interrupt Controller)是ARM公司提供的一個通用的中斷控制器,其architecture specification目前有四個版本,V1~V4(V2最多支援8個ARM core,V3/V4支援更多的ARM core,

ARM-Linux中斷系統

1.前言 瞭解Linux中斷子系統,同時也需要了解ARM體系結構中斷處理流程;在熟悉整個軟硬體架構和流程基礎上,才能對流程進行細化,然後找出問題的瓶頸。《2. 梳理中斷處理子系統》 但是所有的優化都離不開一個量化的過程,有個可靠、高效、可讀性強的度量必不可少。《3. 一種測量中斷效能手段》 最後基於此,進行中

NVIC中斷優先順序管理+串列埠通訊基本原理+串列埠通訊基於庫函式的配置例項

沒寫部落格的感悟:昨天沒有寫部落格,今天就倒黴了,得寫兩篇,果然不能偷懶,當天沒有做的事,無論如何你都得要做,為了改掉這個拖延的小毛病,給自己定了一條規則,無論多晚,哪怕沒有網沒有電也得寫完每天更新的部落格,以此勉勵。 今天主要總結和複習三個知識點,NVIC中斷優先順序管理

ARM異常中斷返回的幾種情況

重要基礎知識:R15(PC)總是指向“正在取指”的指令,而不是指向“正在執行”的指令或正在“譯碼”的指令。一般來說,人們習慣性約定將“正在執行的指令作為參考點”,稱之為當前第一條指令,因此 PC總是指向第三條指令。當 ARM 狀態時,每條指令為 4 位元組長,所以 PC 始

STM32中斷優先順序

STM32中有兩個優先順序 Preemption Priority(搶佔優先順序) SubPriority(子優先順序) 1、搶佔優先順序:顧名思義能夠搶先執行任務,即打斷當前的主程式或者中斷程式的執行,前去完成搶斷中斷。也稱中斷巢狀。 2、子優先順序:也是從優先順序