時序約束(Vivado)

時序約束

本文參考:

《綜合與時序分析的設計約束—Synopsys設計約束(SDC)實用指南》

《vivado從此開始—to learn vivado from here》

一、時鐘週期約束

在設計中說明時鐘的SDC指令是create_clock,該指令的BNF(Backus-Naur Form,巴斯科範式)為:

create_clock -period period_value

[source_objects]

[-name clock_name]

[-waveform edge_list]

[-add]

[-comment comment_string]

1、確定主時鐘

create_clock 的物件必須是主時鐘(Primary clock),通常主時鐘有兩種情況:

- 時鐘由外部時鐘源提供,通過時鐘引腳進入FPGA。

- 高速收發器(GT)的時鐘RXOUTCLK或TXOUTCLK。

vivado 中提供Tcl命令檢視未約束的主時鐘,不過通過vivado提供的時鐘約束嚮導可以快速的完成基本的時序約束工作。

//確定主時鐘

report_clock_networks -name mynetwork

//或者

check_timing -override_defaults no_clock

1)、主時鐘之間有明確的相位關係

假設待約束的時鐘如下:

可表示為:

create_clock -period 10 -name clka - waveform可以省略,預設格式為:{0 週期/2}。有時候需要模擬複雜的波形,比如脈衝消隱,需要在觸發器指定的時間範圍內刪除資料,主要是為了減少射頻干擾。如一下波形:

create_clock -period 10 -name clkb -waveform {3 5 8 9}{get_ports clkb}

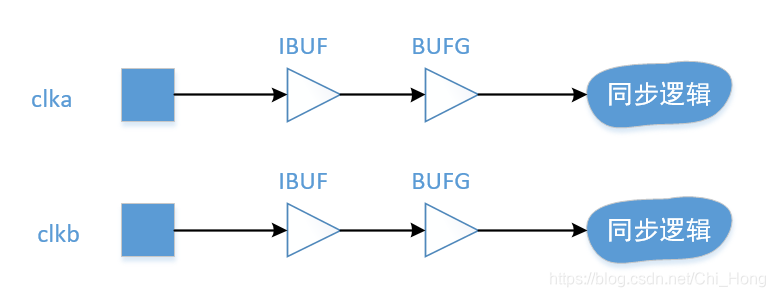

2)、非同步時鐘

非同步時鐘通過set_clock_groups命令指定,如下圖所示的兩個時鐘:

create_clock -period 10 -name clka [get_ports clka]

create_clock -period 5 -name clkb [get_ports clkb]

set_clock_groups -asynchronous -group clka -group clkb

//假如兩個時鐘有生成時鐘的情況

set_clock_groups -asynchronous -group [get_clocks clka -include_generated_clocks] -group [get_clocks clkb -include_generated_clocks]

3)、差分時鐘約束

差分時鐘只約束p埠即可。在一些攝像頭CMOS模組中會遇到的差分時鐘,可以這樣約束:

create_clock -name clkpn -period 5 [get_ports clk_p]

4)、同源多時鐘

有時需要在時鐘源指定多個時鐘,從而滿足多I/O速度協議的需求。有時需要驗證在不同時鐘頻率下的執行情況,也會出現同源多時鐘的情況。

create_clock -name clk_a -period 10 [get_ports clk]

create_clock -name clk_b -period 8 [get_ports clk] -add

每一個時鐘訊號需要一個唯一的名稱來區別。若對同一個物件指定多個時鐘時,沒有指定-add選項,那麼之前的定義會被覆蓋掉。

5)、高速收發時鐘

6)、虛擬時鐘

虛擬時鐘一般只有在建立輸入或輸出延遲的時候才會被使用。分為兩種:

- 傳輸給FPGA的資料所用到的捕獲時鐘是由FPGA內部生成的,與主時鐘頻率不同。

- PCB上有Clock Buffer導致時鐘延遲不同。

//捕獲時鐘是由FPGA內部生成

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name vclk -period 5

set_input_delay 2 -clock vclk [get_ports din]

//PCB上有Clock Buffer導致時鐘延遲不同,假設延遲1ns

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virclk -period 10

set_clock_latency -source 1 [get_clocks virclk]

set_input_delay -clcok virclk -max 4 -min 2 [get_ports din]

二、兩種時序例外

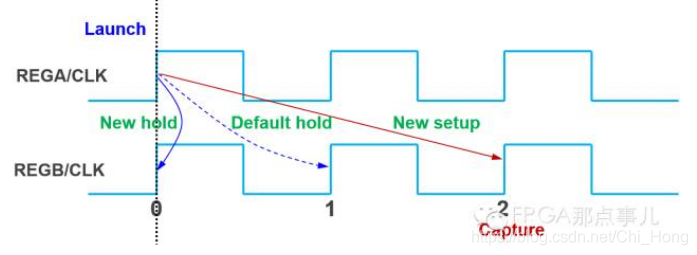

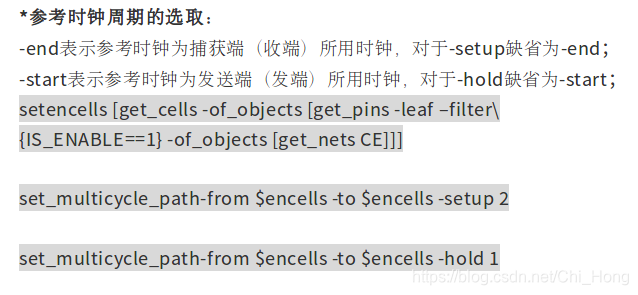

1、多週期路徑

工程實踐中會存在這種情形:資料路徑裸機較為複雜,導致延時過大,使得資料無法在一個週期內穩定下來;或者資料在傳送幾個時鐘週期以後邏輯才使用。設計者的意圖是,從發起沿數個時鐘之後捕獲資料。fpga那點事兒的文章中有這麼個例子:

2、虛假路徑

虛假路徑或稱為偽路徑是指基於該路徑的電路功能不會發生或者該路徑無須時序約束。

set_false_path -from [get_cells {opb_r_reg}] to [get_cells {dout_reg}]